INTEGRATED CIRCUITS

Product specification Supersedes data of November 1994 File under Integrated Circuits, IC03 1995 Jul 06

#### FEATURES

- Low current from 3 V supply

- Fully programmable RF divider

- 3-line serial interface bus

- Second synthesizer to control first IF or offset loop frequency

- Independent fully programmable reference dividers for each loop, driven from external crystal oscillator

- Dual phase detector outputs to allow fast frequency switching

- Dual power-down modes.

#### APPLICATIONS

- 1 to 1.7 GHz mobile telephones

- Portable battery-powered radio equipment.

#### **GENERAL DESCRIPTION**

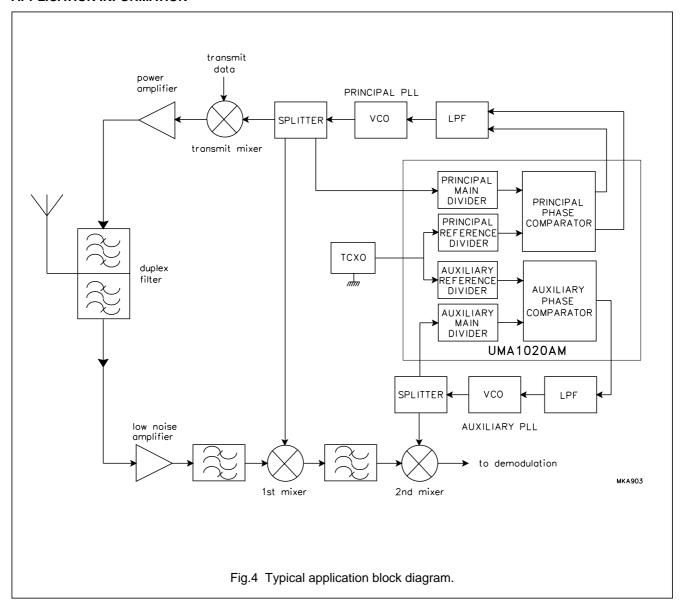

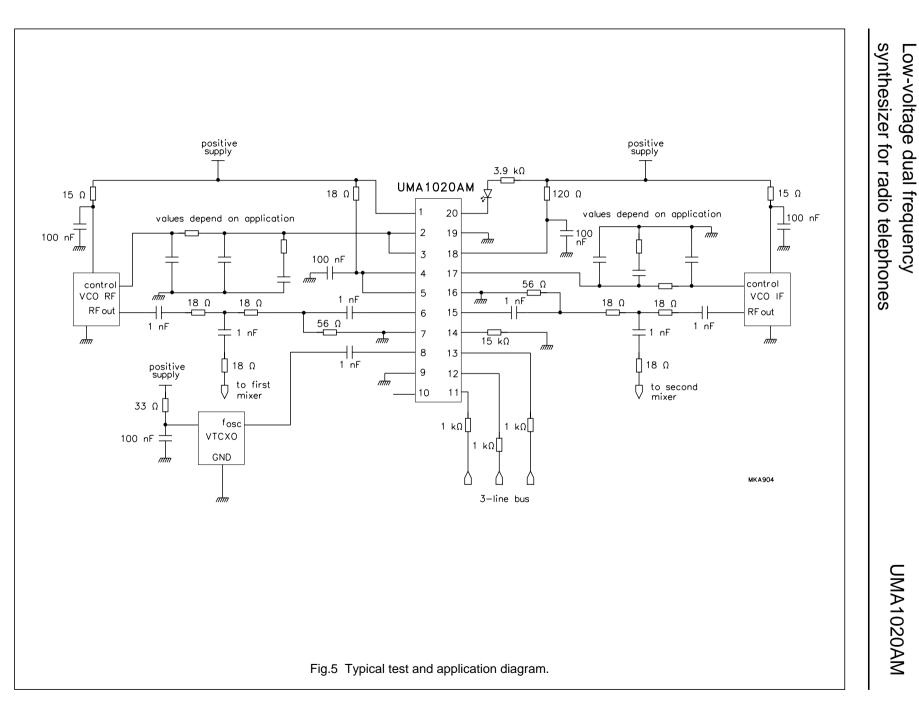

The UMA1020AM BICMOS device integrates prescalers, programmable dividers, and phase comparators to implement two phase-locked loops. The device is designed to operate from 3 NiCd cells, in pocket phones, with low current and nominal 5 V supplies.

#### The principal synthesizer operates at RF input frequencies up to 1.7 GHz the auxiliary synthesizer operates at 300 MHz. The auxiliary loop is intended for the first IF or to transmit offset loop-frequency settings. Each synthesizer has a fully programmable reference divider. All divider ratios are supplied via a 3-wire serial programming bus.

Separate power and ground pins are provided to the analog and digital circuits. The ground leads should be externally short-circuited to prevent large currents flowing across the die and thus causing damage. Digital supplies  $V_{DD1}$  and  $V_{DD2}$  must also be at the same potential.  $V_{CC}$  must be equal to or greater than  $V_{DD}$  (i.e.  $V_{DD} = 3$  V and  $V_{CC} = 5$  V for wider tuning range).

The principal synthesizer phase detector uses two charge pumps, one provides normal loop feedback, while the other is only active during fast mode to speed-up switching. The auxiliary loop has a separate phase detector. All charge pump currents (gain) are fixed by an external resistance at pin  $I_{SET}$  (pin 14). Only passive loop filters are used; the charge-pumps function within a wide voltage compliance range to improve the overall system performance.

#### QUICK REFERENCE DATA

| SYMBOL                                | PARAMETER                                          | CONDITIONS                               | MIN. | TYP. | MAX. | UNIT |

|---------------------------------------|----------------------------------------------------|------------------------------------------|------|------|------|------|

| V <sub>CC</sub> , V <sub>DD</sub>     | supply voltage                                     | $V_{CC} \ge V_{DD}$                      | 2.7  | -    | 5.5  | V    |

| I <sub>CC</sub> + I <sub>DD</sub>     | principal synthesizer supply current               | auxiliary synthesizer in power-down mode | -    | 9.4  | -    | mA   |

|                                       | principal and auxiliary synthesizer supply current | principal and auxiliary synthesizers ON  | -    | 12.1 | -    | mA   |

| I <sub>CCPD</sub> , I <sub>DDPD</sub> | current in power-down mode per supply              |                                          | -    | 12   | _    | μA   |

| f <sub>VCO</sub>                      | principal input frequency                          |                                          | 1000 | 1500 | 1700 | MHz  |

| f <sub>AI</sub>                       | auxiliary input frequency                          |                                          | 20   | _    | 300  | MHz  |

| f <sub>XTAL</sub>                     | crystal reference input frequency                  |                                          | 3    | -    | 40   | MHz  |

| f <sub>PPC</sub>                      | principal phase comparator frequency               |                                          | _    | 200  | _    | kHz  |

| f <sub>APC</sub>                      | auxiliary phase comparator frequency               |                                          | -    | 200  | _    | kHz  |

| T <sub>amb</sub>                      | operating ambient temperature                      |                                          | -30  | -    | +85  | °C   |

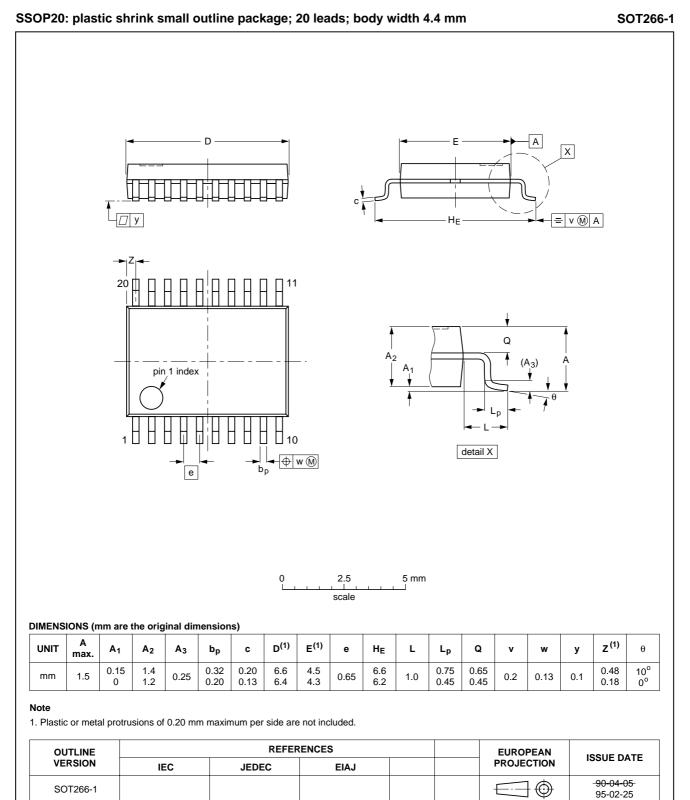

#### **ORDERING INFORMATION**

| TYPE      | PACKAGE |                                                                   |          |

|-----------|---------|-------------------------------------------------------------------|----------|

| NUMBER    | NAME    | DESCRIPTION                                                       | VERSION  |

| UMA1020AM | SSOP20  | plastic shrink small outline package; 20 leads; body width 4.4 mm | SOT266-1 |

### UMA1020AM

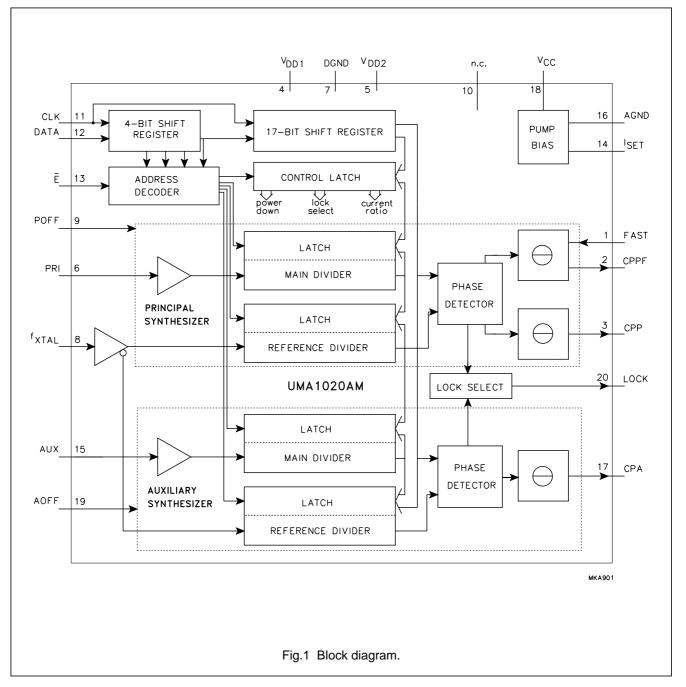

#### **BLOCK DIAGRAM**

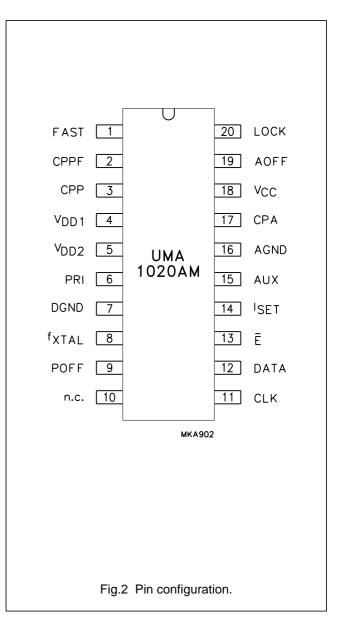

#### PINNING

| SYMBOL            | PIN | DESCRIPTION                                          |

|-------------------|-----|------------------------------------------------------|

| FAST              | 1   | control input to speed-up main synthesizer           |

| CPPF              | 2   | principal synthesizer speed-up<br>charge-pump output |

| CPP               | 3   | principal synthesizer normal<br>charge-pump output   |

| V <sub>DD1</sub>  | 4   | digital power supply 1                               |

| V <sub>DD2</sub>  | 5   | digital power supply 2                               |

| PRI               | 6   | 1.7 GHz principal synthesizer<br>frequency input     |

| DGND              | 7   | digital ground                                       |

| f <sub>XTAL</sub> | 8   | common crystal frequency input from TCXO             |

| POFF              | 9   | principal synthesizer power-down input               |

| n.c.              | 10  | not connected                                        |

| CLK               | 11  | programming bus clock input                          |

| DATA              | 12  | programming bus data input                           |

| Ē                 | 13  | programming bus enable input<br>(active LOW)         |

| I <sub>SET</sub>  | 14  | regulator pin to set the charge-pump currents        |

| AUX               | 15  | auxiliary synthesizer frequency input                |

| AGND              | 16  | analog ground                                        |

| СРА               | 17  | auxiliary synthesizer charge-pump output             |

| V <sub>CC</sub>   | 18  | supply for charge-pump                               |

| AOFF              | 19  | auxiliary synthesizer power-down input               |

| LOCK              | 20  | in-lock detect output (main PLL); test mode output   |

#### FUNCTIONAL DESCRIPTION

#### **Principal synthesizer**

Programmable reference and main dividers drive the principal PLL phase detector. Two charge pumps produce phase error current pulses for integration in an external loop filter. A hardwired power-down input POFF (pin 9) ensures that the dividers and phase comparator circuits can be disabled.

The PRI input (pin 6) drives a preamplifier to provide the clock to the first divider stage. The preamplifier has a high input impedance, dominated by pin and pad capacitance. The circuit operates with signal levels from 100 mV to 500 mV (RMS), and at frequencies up to 1.7 GHz. The high frequency divider circuits use bipolar transistors, slower bits are CMOS. Divider ratios (512 to 131071) allow up to 2 MHz phase comparison frequency.

The reference and main divider outputs are connected to a phase/frequency detector that controls two charge pumps. The two pumps have a common bias-setting current that is set by an external resistance. The ratio between currents in fast and normal operating modes can be programmed via the 3-wire serial bus. The low current pump remains active except in power-down. The high current pump is enabled via the control input FAST (pin 1). By appropriate connection to the loop filter, dual bandwidth loops are provided: short time constant during frequency switching (FAST mode) to speed-up channel changes and low bandwidth in the settled state (on-frequency) to reduce noise and breakthrough levels.

The principal synthesizer speed-up charge pump (CPPF) is controlled by the FAST input in synchronization with phase detector operation in such a way that potential disturbances are minimized. The dead zone (caused by finite time taken to switch the current sources on or off) is cancelled by feedback from the normal pump output to the phase detector thereby improving linearity.

An open drain transistor drives the output pin LOCK (pin 20). It is recommended that the pull-up resistor from this pin to  $V_{DD}$  is chosen such that the value is high enough to keep the sink current in the LOW state below 400  $\mu$ A. The circuit can be programmed to output either the phase error in the principal or auxiliary phase detectors or the combination from both detectors (OR function). The resultant output will be a current pulse with the duration of the selected phase error. By appropriate external filtering and threshold comparison, an out-of-lock or an in-lock flag is generated.

#### Auxiliary synthesizer

The auxiliary synthesizer has a 14-bit main divider and an 11-bit reference divider. A separate power-down input AOFF (pin 19), disables currents in the auxiliary dividers, phase detector, and charge pump. The auxiliary input signal is amplified and fed to the main divider. The input buffer presents a high impedance, dominated by pin and pad capacitance. First divider stages use bipolar technology operating at input frequencies up to 300 MHz; the slower bits are CMOS. The auxiliary loop phase detector and charge pump use similar circuits to the main loop low-current phase comparator, including dead-zone compensation feedback.

The auxiliary reference divider is clocked on the opposite edge of the principal reference divider to ensure that active edges arrive at the auxiliary and principal phase detectors at different times. This minimizes the potential for interference between the charge pumps of each loop.

### **UMA1020AM**

Product specification

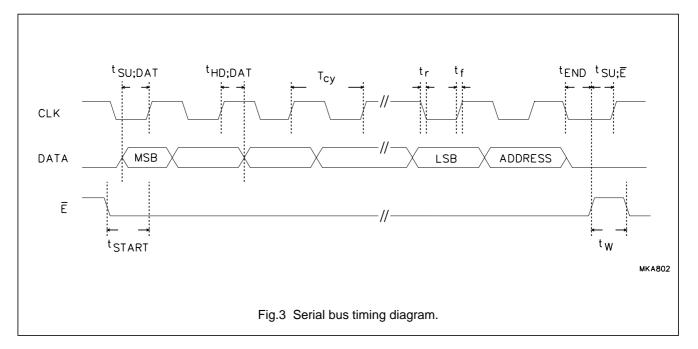

#### Serial programming bus

A simple 3-line unidirectional serial bus is used to program the circuit. The 3 lines are DATA, CLK and  $\overline{E}$  (enable). The data sent to the device is loaded in bursts framed by  $\overline{E}$ . Programming clock edges and their appropriate data bits are ignored until  $\overline{E}$  goes active LOW. The programmed information is loaded into the addressed latch when  $\overline{E}$ returns inactive HIGH. Only the last 21 bits serially clocked into the device are retained within the programming register. Additional leading bits are ignored, and no check is made on the number of clock pulses. The fully static CMOS design uses virtually no current when the bus is inactive. It can always capture new programmed data even during power-down of main and auxiliary loops.

However when either principal synthesizer or auxiliary synthesizer or both are powered-on, the presence of a TCXO signal is required at pin 8 ( $f_{XTAL}$ ) for correct programming.

#### Data format

Data is entered with the most significant bit first. The leading bits make up the data field, while the trailing four bits are an address field. The UMA1020AM uses 5 of the 16 available addresses. The data format is shown in Table 1. The first entered bit is p1, the last bit is p21.

The trailing address bits are decoded on the inactive edge of  $\overline{E}$ . This produces an internal load pulse to store the data in one of the addressed latches. To ensure that the data is correctly loaded on first power-up,  $\overline{E}$  should be held LOW and only taken HIGH after having programmed an appropriate register. To avoid erroneous divider ratios, the pulse is not allowed during data reads by the frequency dividers.

This condition is guaranteed by respecting a minimum E pulse width after data transfer. The corresponding relationship between data fields and addresses is given in Table 2.

Philips Semiconductors

# synthesizer for radio telephones Low-voltage dual frequency

**UMA1020AM**

#### p16 p2 p17 ../.. ADD3 ../.. ADD0 ADD1 ADD2 DATA0 DATA1 DATA15 DATA COEFFICIENT LATCH ADDRESS LSB FT **REGISTER BIT ALLOCATION** p18 p19 p20 p2 p10 p12 p13 p16 p17 p1 p3 p4 p5 p6 p7 p8 p9 p11 p14 p15 dt14 dt13 dt12 DATA FIELD dt3 dt2 dt1 ADDRESS dt4 dt16 dt15 dt0 TEST BITS<sup>(2)</sup> 0 0 OLP OLA CR1 CR0 X sPOFF sAOFF X Х X Х Х Х Х Х Х Х 0 0 PM16 PRINCIPAL MAIN DIVIDER COEFFICIENT PM0 0 1

PRINCIPAL REFERENCE DIVIDER COEFFICIENT Х Х Х Х Х **PR10** PR0 0 1 AM13 Х Х AUXILIARY MAIN DIVIDER COEFFICIENT AM0 0 1 Х Х Х Х Х AR10 AUXILIARY REFERENCE DIVIDER COEFFICIENT AR0 0 1

ი Notes

Х

Х

Х

- 1. FT = first, LT = last; sPOFF = software power-down for principal synthesizer (1 = OFF); sAOFF = software power-down for auxiliary synthesizer (1 = OFF).

- 2. The test register should not be programmed with any other value except all zeros for normal operation.

#### Table 3 Out-of-lock select

| OLP | OLA | OUT-OF-LOCK ON PIN 20        |

|-----|-----|------------------------------|

| 0   | 0   | output disabled              |

| 0   | 1   | auxiliary phase error        |

| 1   | 0   | principal phase error        |

| 1   | 1   | both auxiliary and principal |

# 1995 Jul 06

Table 1

Format of programmed data

LAST IN PROGRAMMING REGISTER BIT USAGE p21 p20 p19 p18

#### Table 2 Bit allocation (note 1)

Product specification

**FIRST IN**

p1

DATA16

MSB

0

0

0

0

1

1

LT

p21

0

1

0

1

0

1

### UMA1020AM

| CR1 | CR0 | I <sub>CPA</sub>         | I <sub>CPP</sub>          | I <sub>CPPF</sub>         | I <sub>CPPF</sub> : I <sub>CPP</sub> |

|-----|-----|--------------------------|---------------------------|---------------------------|--------------------------------------|

| 0   | 0   | $4 	imes I_{\text{SET}}$ | $4 	imes I_{\text{SET}}$  | $16 	imes I_{SET}$        | 4 : 1                                |

| 0   | 1   | $4 	imes I_{\text{SET}}$ | $4 	imes I_{\text{SET}}$  | $32 	imes I_{SET}$        | 8 : 1                                |

| 1   | 0   | $4 	imes I_{\text{SET}}$ | $2 \times I_{SET}$        | $24 	imes I_{\text{SET}}$ | 12 : 1                               |

| 1   | 1   | $4 	imes I_{\text{SET}}$ | $2 \times I_{\text{SET}}$ | $32 	imes I_{SET}$        | 16 : 1                               |

#### Table 4 Fast and normal charge pumps current ratio (note 1)

Note

1.  $I_{SET} = \frac{V_{14}}{R_{ext}}$ ; common bias current for charge pumps.

#### Table 5 Power-down modes

| AOFF | POFF | FAST | PRINCIPAL<br>DIVIDERS | AUXILIARY<br>DIVIDERS | PUMP<br>CPA | PUMP<br>CPP | PUMP<br>CPPF |

|------|------|------|-----------------------|-----------------------|-------------|-------------|--------------|

| 1    | 1    | Х    | OFF                   | OFF                   | OFF         | OFF         | OFF          |

| 1    | 0    | 0    | ON                    | OFF                   | OFF         | ON          | OFF          |

| 1    | 0    | 1    | ON                    | OFF                   | OFF         | ON          | ON           |

| 0    | 1    | Х    | OFF                   | ON                    | ON          | OFF         | OFF          |

| 0    | 0    | 0    | ON                    | ON                    | ON          | ON          | OFF          |

| 0    | 0    | 1    | ON                    | ON                    | ON          | ON          | ON           |

#### Power-down modes

The action of the control inputs on the state of internal blocks is defined by Table 5.

Note that in Table 5, POFF and AOFF can be either the software or hardware power-down signals. The dividers are ON when both hardware and software power-down signals are at logic 0.

When either synthesizer is reactivated after power-down the main and reference dividers of that synthesizer are synchronized to avoid the possibility of random phase errors on power-up.

#### LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL                | PARAMETER                                                                             | MIN. | MAX.                  | UNIT |

|-----------------------|---------------------------------------------------------------------------------------|------|-----------------------|------|

| V <sub>DD</sub>       | digital supply voltage                                                                | -0.3 | +5.5                  | V    |

| V <sub>CC</sub>       | analog supply voltage                                                                 | -0.3 | +5.5                  | V    |

| $\Delta V_{CC-DD}$    | difference in voltage between $V_{CC}$ and $V_{DD}$                                   | -0.3 | +5.5                  | V    |

| V <sub>n</sub>        | voltage at pins 1, 6, 8 to 15, 19 and 20                                              | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| V <sub>2, 3, 17</sub> | voltage at pins 2, 3 and 17                                                           | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| $\Delta V_{GND}$      | difference in voltage between AGND and DGND (these pins should be connected together) | -0.3 | +0.3                  | V    |

| P <sub>tot</sub>      | total power dissipation                                                               | -    | 150                   | mW   |

| T <sub>stg</sub>      | storage temperature                                                                   | -55  | +125                  | °C   |

| T <sub>amb</sub>      | operating ambient temperature                                                         | -30  | +85                   | °C   |

| Tj                    | maximum junction temperature                                                          | -    | 95                    | °C   |

#### HANDLING

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling MOS devices.

#### THERMAL CHARACTERISTICS

| SYMBOL              | PARAMETER                                               | VALUE | UNIT |

|---------------------|---------------------------------------------------------|-------|------|

| R <sub>th j-a</sub> | thermal resistance from junction to ambient in free air | 120   | K/W  |

### UMA1020AM

#### CHARACTERISTICS

$V_{DD1}$  =  $V_{DD2}$  = 2.7 to 5.5 V;  $V_{CC}$  = 2.7 to 5.5 V;  $T_{amb}$  = 25 °C; unless otherwise specified.

| SYMBOL                                | PARAMETER                                      | CONDITIONS                                                | MIN.     | TYP. | MAX.   | UNIT |

|---------------------------------------|------------------------------------------------|-----------------------------------------------------------|----------|------|--------|------|

| Supply; pins                          | s 4, 5 and 18                                  |                                                           | <b>!</b> | •    | •      | •    |

| V <sub>DD</sub>                       | digital supply voltage                         | $V_{DD1} = V_{DD2}$                                       | 2.7      | -    | 5.5    | V    |

| V <sub>CC</sub>                       | analog supply voltage                          | $V_{CC} \ge V_{DD}$                                       | 2.7      | _    | 5.5    | V    |

| I <sub>DD</sub>                       | principal synthesizer digital supply current   | V <sub>DD</sub> = 5.5 V                                   | -        | 9    | 11     | mA   |

|                                       | auxiliary synthesizer digital supply current   | V <sub>DD</sub> = 5.5 V                                   | -        | 2.7  | 4.0    | mA   |

| I <sub>CC</sub>                       | charge pumps supply current                    | V <sub>CC</sub> = 5.5 V;<br>R <sub>ext</sub> =12 kΩ       | -        | 0.4  | 1.0    | mA   |

| I <sub>CCPD</sub> , I <sub>DDPD</sub> | current in power-down mode per supply          | logic levels 0 or $V_{DD}$                                | -        | 12   | 50     | μA   |

| RF principa                           | l main divider input; pin 6                    |                                                           |          |      |        |      |

| f <sub>VCO</sub>                      | RF input frequency                             |                                                           | 1000     | 1500 | 1700   | MHz  |

| V <sub>6(rms)</sub>                   | AC-coupled input signal level (RMS value)      | R <sub>s</sub> = 50 Ω                                     | 100      | -    | 500    | mV   |

| ZI                                    | input impedance (real part)                    | f <sub>VCO</sub> = 1.7 GHz                                | -        | 300  | _      | Ω    |

| Cl                                    | typical pin input capacitance                  | indicative, not tested                                    | -        | 2    | -      | pF   |

| R <sub>pm</sub>                       | principal main divider ratio                   |                                                           | 512      | -    | 131071 |      |

| f <sub>PPCmax</sub>                   | maximum principal phase comparator frequency   |                                                           | -        | 2000 | -      | kHz  |

| f <sub>PPCmin</sub>                   | minimum principal phase comparator frequency   |                                                           | -        | 10   | -      | kHz  |

| Auxiliary ma                          | ain divider input; pin 15                      |                                                           |          | •    | •      |      |

| f <sub>AI</sub>                       | input frequency                                |                                                           | 20       | -    | 300    | MHz  |

| V <sub>15(rms)</sub>                  | AC-coupled input signal level (RMS value)      | R <sub>s</sub> = 50 Ω;<br>2.7 V < V <sub>DD</sub> < 3.5 V | 50       | -    | 500    | mV   |

|                                       |                                                | R <sub>s</sub> = 50 Ω;<br>3.5 V < V <sub>DD</sub> < 5.5 V | 100      | -    | 500    | mV   |

| ZI                                    | input impedance (real part)                    | f <sub>AI</sub> = 100 MHz                                 | -        | 1    | -      | kΩ   |

| CI                                    | typical pin input capacitance                  | indicative, not tested                                    | -        | 2    | -      | pF   |

| R <sub>am</sub>                       | auxiliary main divider ratio                   |                                                           | 64       | -    | 16383  |      |

| f <sub>APCmax</sub>                   | maximum auxiliary loop<br>comparison frequency |                                                           | -        | 2000 | -      | kHz  |

| f <sub>APCmin</sub>                   | minimum auxiliary loop<br>comparison frequency |                                                           | -        | 10   | -      | kHz  |

| SYMBOL              | PARAMETER                                        | CONDITIONS                         | MIN.               | TYP. | MAX.                  | UNIT |

|---------------------|--------------------------------------------------|------------------------------------|--------------------|------|-----------------------|------|

| Crystal refe        | rence dividers input; pin 8                      |                                    |                    |      | 1                     |      |

| f <sub>XTAL</sub>   | crystal reference input frequency                |                                    | 3                  | -    | 40                    | MHz  |

| V <sub>8(rms)</sub> | sinusoidal input signal level                    | 5 MHz < f <sub>XTAL</sub> < 40 MHz | 50                 | -    | 500                   | mV   |

|                     | (RMS value)                                      | 3 MHz < f <sub>XTAL</sub> < 40 MHz | 100                | -    | 500                   | mV   |

| ZI                  | input impedance (real part)                      | f <sub>XTAL</sub> = 30 MHz         | -                  | 2    | _                     | kΩ   |

| Cl                  | typical pin input capacitance                    | indicative, not tested             | -                  | 2    | _                     | pF   |

| R <sub>pr</sub>     | principal reference divider ratio                |                                    | 8                  | -    | 2047                  |      |

| R <sub>ar</sub>     | auxiliary reference divider ratio                |                                    | 8                  | -    | 2047                  |      |

| Charge pun          | np current setting resistor input; p             | in 14                              |                    |      |                       | •    |

| R <sub>ext</sub>    | external resistor from pin 14 to ground          |                                    | 12                 | -    | 60                    | kΩ   |

| V <sub>14</sub>     | regulated voltage at pin 14                      | $R_{ext} = 12 k\Omega$             | -                  | 1.15 | _                     | V    |

| Charge pun          | np outputs; pins 17, 3 and 2; R <sub>ext</sub> = | <b>- 12 k</b> Ω                    |                    |      |                       |      |

| I <sub>Ocp</sub>    | charge pump output current error                 |                                    | -25                | -    | +25                   | %    |

| I <sub>match</sub>  | sink-to-source current matching                  | V <sub>cp</sub> in range           | -                  | ±5   | _                     | %    |

| ILcp                | charge pump off leakage current                  | $V_{cp} = \frac{1}{2}V_{CC}$       | -5                 | ±1   | +5                    | nA   |

| V <sub>cp</sub>     | charge pump voltage compliance                   |                                    | 0.4                | -    | V <sub>CC</sub> - 0.4 | V    |

| Interface lo        | gic input signal levels; pins 13, 12             | , 11 and 1                         |                    |      |                       | •    |

| V <sub>IH</sub>     | HIGH level input voltage                         |                                    | 0.7V <sub>DD</sub> | -    | V <sub>DD</sub> + 0.3 | V    |

| V <sub>IL</sub>     | LOW level input voltage                          |                                    | -0.3               | -    | 0.3V <sub>DD</sub>    | V    |

| I <sub>bias</sub>   | input bias current                               | logic 1 or logic 0                 | -5                 | -    | +5                    | μA   |

| Cl                  | input capacitance                                | indicative, not tested             | -                  | 2    | -                     | pF   |

| Lock detect         | output signal; pin 20 open-drain o               | output                             |                    |      |                       |      |

| V <sub>OL</sub>     | LOW level output voltage                         | I <sub>sink</sub> = 0.4 mA         | _                  | _    | 0.4                   | V    |

#### SERIAL BUS TIMING CHARACTERISTICS

$V_{DD}$  =  $V_{CC}$  = 3 V;  $T_{amb}$  = 25  $^\circ C$  unless otherwise specified.

| SYMBOL                        | PARAMETER                             | MIN.                | TYP. | MAX. | UNIT |  |

|-------------------------------|---------------------------------------|---------------------|------|------|------|--|

| Serial programming clock; CLK |                                       |                     |      |      |      |  |

| t <sub>r</sub>                | input rise time                       | _                   | 10   | 40   | ns   |  |

| t <sub>f</sub>                | input fall time                       | _                   | 10   | 40   | ns   |  |

| T <sub>cy</sub>               | clock period                          | 100                 | -    | -    | ns   |  |

| Enable progra                 | Enable programming; E                 |                     |      |      |      |  |

| t <sub>START</sub>            | delay to rising clock edge            | 40                  | -    | -    | ns   |  |

| t <sub>END</sub>              | delay from last falling clock edge    | -20                 | -    | -    | ns   |  |

| t <sub>W</sub>                | minimum inactive pulse width          | 4000 <sup>(1)</sup> | -    | -    | ns   |  |

| t <sub>SU;Ē</sub>             | enable set-up time to next clock edge | 20                  | -    | -    | ns   |  |

| Register seria                | Register serial input data; DATA      |                     |      |      |      |  |

| t <sub>SU;DAT</sub>           | input data to clock set-up time       | 20                  | -    | -    | ns   |  |

| t <sub>HD;DAT</sub>           | input data to clock hold time         | 20                  | -    | -    | ns   |  |

#### Note

1. The minimum pulse width  $(t_W)$  can be smaller than 4  $\mu$ s provided all the following conditions are satisfied:

- a) Principal main divider input frequency  $f_{VCO} > \frac{512}{t_W}$

- b) Auxiliary main divider input frequency  $f_{AI} > \frac{32}{t_W}$

**UMA1020AM**

# Low-voltage dual frequency synthesizer for radio telephones

### APPLICATION INFORMATION

Philips Semiconductors

Product specification

1995 Jul 06

ώ

#### PACKAGE OUTLINE

#### SOLDERING SO or SSOP

#### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these cases reflow soldering is often used.

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our *"IC Package Databook"* (order code 9398 652 90011).

#### **Reflow soldering**

Reflow soldering techniques are suitable for all SO and SSOP packages.

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several techniques exist for reflowing; for example, thermal conduction by heated belt. Dwell times vary between 50 and 300 seconds depending on heating method. Typical reflow temperatures range from 215 to 250 °C.

Preheating is necessary to dry the paste and evaporate the binding agent. Preheating duration: 45 minutes at 45 °C.

#### Wave soldering

#### SO

Wave soldering techniques can be used for all SO packages if the following conditions are observed:

- A double-wave (a turbulent wave with high upward pressure followed by a smooth laminar wave) soldering technique should be used.

- The longitudinal axis of the package footprint must be parallel to the solder flow.

- The package footprint must incorporate solder thieves at the downstream end.

#### SSOP

Wave soldering is **not** recommended for SSOP packages. This is because of the likelihood of solder bridging due to closely-spaced leads and the possibility of incomplete solder penetration in multi-lead devices.

### If wave soldering cannot be avoided, the following conditions must be observed:

- A double-wave (a turbulent wave with high upward pressure followed by a smooth laminar wave) soldering technique should be used.

- The longitudinal axis of the package footprint must be parallel to the solder flow and must incorporate solder thieves at the downstream end.

Even with these conditions, only consider wave soldering SSOP packages that have a body width of 4.4 mm, that is SSOP16 (SOT369-1) or SSOP20 (SOT266-1).

#### METHOD (SO OR SSOP)

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Maximum permissible solder temperature is 260 °C, and maximum duration of package immersion in solder is 10 seconds, if cooled to less than 150 °C within 6 seconds. Typical dwell time is 4 seconds at 250 °C.

A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

#### **Repairing soldered joints**

Fix the component by first soldering two diagonallyopposite end leads. Use only a low voltage soldering iron (less than 24 V) applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C. When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds at 270 to 320 °C.

#### DEFINITIONS

| Data sheet status                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                       |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|

| Objective specification                                                                                                                                                                                                                                                                                                                                                                                                                                   | This data sheet contains target or goal specifications for product development.       |  |  |  |

| Preliminary specification                                                                                                                                                                                                                                                                                                                                                                                                                                 | This data sheet contains preliminary data; supplementary data may be published later. |  |  |  |

| Product specification                                                                                                                                                                                                                                                                                                                                                                                                                                     | This data sheet contains final product specifications.                                |  |  |  |

| Limiting values                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                       |  |  |  |

| Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability. |                                                                                       |  |  |  |

| Application information                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                       |  |  |  |

Where application information is given, it is advisory and does not form part of the specification.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

### UMA1020AM

NOTES

### UMA1020AM

NOTES

### UMA1020AM

NOTES

### Philips Semiconductors – a worldwide company

Argentina: IEROD, Av. Juramento 1992 - 14.b, (1428) BUENOS AIRES, Tel. (541)786 7633, Fax. (541)786 9367 Australia: 34 Waterloo Road, NORTH RYDE, NSW 2113, Tel. (02)805 4455, Fax. (02)805 4466 Austria: Triester Str. 64, A-1101 WIEN, P.O. Box 213, Tel. (01)60 101-1236, Fax. (01)60 101-1211 Belgium: Postbus 90050, 5600 PB EINDHOVEN, The Netherlands, . Tel. (31)40 783 749, Fax. (31)40 788 399 Brazil: Rua do Rocio 220 - 5<sup>th</sup> floor, Suite 51, CEP: 04552-903-SÃO PAULO-SP, Brazil. P.O. Box 7383 (01064-970) Tel. (011)821-2333, Fax. (011)829-1849 Canada: PHILIPS SEMICONDUCTORS/COMPONENTS: Tel. (800) 234-7381, Fax. (708) 296-8556 Chile: Av. Santa Maria 0760, SANTIAGO, Tel. (02)773 816, Fax. (02)777 6730 China/Hong Kong: 501 Hong Kong Industrial Technology Centre, 72 Tat Chee Ävenue, Kowloon Tong, HONG KONG, Tel. (852)2319 7888, Fax. (852)2319 7700 Colombia: IPRELENSO LTDA, Carrera 21 No. 56-17, 77621 BOGOTA, Tel. (571)249 7624/(571)217 4609, Fax. (571)217 4549 Denmark: Prags Boulevard 80, PB 1919, DK-2300 COPENHAGEN S, Tel. (032)88 2636, Fax. (031)57 1949 Finland: Sinikalliontie 3, FIN-02630 ESPOO Tel. (358)0-615 800, Fax. (358)0-61580 920 France: 4 Rue du Port-aux-Vins, BP317, 92156 SURESNES Cedex Tel. (01)4099 6161, Fax. (01)4099 6427 Germany: P.O. Box 10 63 23, 20043 HAMBURG, Tel. (040)3296-0, Fax. (040)3296 213. Greece: No. 15, 25th March Street, GR 17778 TAVROS. Tel. (01)4894 339/4894 911, Fax. (01)4814 240 India: Philips INDIA Ltd, Shivsagar Estate, A Block, Dr. Annie Besant Rd. Worli, Bombay 400 018 Tel. (022)4938 541, Fax. (022)4938 722 Indonesia: Philips House, Jalan H.R. Rasuna Said Kav. 3-4, P.O. Box 4252, JAKARTA 12950, Tel. (021)5201 122, Fax. (021)5205 189 Ireland: Newstead, Clonskeagh, DUBLIN 14, Tel. (01)7640 000, Fax. (01)7640 200 Italy: PHILIPS SEMICONDUCTORS S.r.I. Piazza IV Novembre 3, 20124 MILANO Tel. (0039)2 6752 2531, Fax. (0039)2 6752 2557 Japan: Philips Bldg 13-37, Kohnan 2-chome, Minato-ku, TOKYO 108, Tel. (03)3740 5130, Fax. (03)3740 5077 Korea: Philips House, 260-199 Itaewon-dong, Yongsan-ku, SEOUL, Tel. (02)709-1412, Fax. (02)709-1415 Malaysia: No. 76 Jalan Universiti, 46200 PETALING JAYA, SELANGOR, Tel. (03)750 5214, Fax. (03)757 4880 Mexico: 5900 Gateway East, Suite 200, EL PASO, TX 79905, Tel. 9-5(800)234-7381, Fax. (708)296-8556 Netherlands: Postbus 90050, 5600 PB EINDHOVEN, Bldg. VB, Tel. (040)783749, Fax. (040)788399 (From 10-10-1995: Tel. (040)2783749, Fax. (040)2788399) New Zealand: 2 Wagener Place, C.P.O. Box 1041, AUCKLAND, Tel. (09)849-4160, Fax. (09)849-7811 Norway: Box 1, Manglerud 0612, OSLO, Tel. (022)74 8000, Fax. (022)74 8341

Pakistan: Philips Electrical Industries of Pakistan Ltd., Exchange Bldg. ST-2/A, Block 9, KDA Scheme 5, Clifton, KARACHI 75600, Tel. (021)587 4641-49, Fax. (021)577035/5874546 Philippines: PHILIPS SEMICONDUCTORS PHILIPPINES Inc, 106 Valero St. Salcedo Village, P.O. Box 2108 MCC, MAKATI, Metro MANILA, Tel. (02)810 0161, Fax. (02)817 3474 Portugal: PHILIPS PORTUGUESA, S.A. Rua dr. António Loureiro Borges 5, Arquiparque - Miraflores, Apartado 300, 2795 LINDA-A-VELHA, Tel. (01)4163160/4163333, Fax. (01)4163174/4163366 Singapore: Lorong 1, Toa Payoh, SINGAPORE 1231, Tel. (65)350 2000, Fax. (65)251 6500 South Africa: S.A. PHILIPS Pty Ltd. 195-215 Main Road Martindale, 2092 JOHANNESBURG, P.O. Box 7430, Johannesburg 2000, Tel. (011)470-5911, Fax. (011)470-5494. Spain: Balmes 22, 08007 BARCELONA Spain: Ballies 22, 06007 DARCELONA, Tel. (03)301 6312, Fax. (03)301 42 43

Sweden: Kottbygatan 7, Akalla. S-164 85 STOCKHOLM, Tel. (0)8-632 2000, Fax. (0)8-632 2745 Switzerland: Allmendstrasse 140, CH-8027 ZÜRICH, Tel. (01)488 2211, Fax. (01)481 77 30 Taiwan: PHILIPS TAIWAN Ltd., 23-30F, 66, Chung Hsiao West Road, Sec. 1. Taipeh, Taiwan ROC, P.O. Box 22978, TAIPEI 100, Tel. (02)388 7666, Fax. (02)382 4382 Thailand: PHILIPS ELECTRONICS (THAILAND) Ltd., 209/2 Sanpavuth-Bangna Road Prakanong, Bangkok 10260, THAILAND, Tel. (662)398-0141, Fax. (662)398-3319 Turkey: Talatpasa Cad. No. 5, 80640 GÜLTEPE/ISTANBUL, Tel. (0212)279 27 70, Fax. (0212)282 67 07 United Kingdom: Philips Semiconductors LTD. 276 Bath Road, Hayes, MIDDLESEX UB3 5BX Tel. (0181)730-5000, Fax. (0181)754-8421 United States: 811 East Arques Avenue, SUNNYVALE, CA 94088-3409, Tel. (800)234-7381, Fax. (708)296-8556 Uruguay: Coronel Mora 433, MONTEVIDEO, Tel. (02)70-4044, Fax. (02)92 0601 Internet: http://www.semiconductors.philips.com/ps/ For all other countries apply to: Philips Semiconductors, International Marketing and Sales, Building BE-p,

P.O. Box 218, 5600 MD EINDHOVEN, The Netherlands, Telex 35000 phtcnl, Fax. +31-40-724825 (from 10-10-1995: +31-40-2724825)

SCD41 © Philips Electronics N.V. 1995

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Printed in The Netherlands

413061/1500/02/pp20 Document order number: Date of release: 1995 Jul 06 9397 750 00194

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.