August 2001 Revised August 2001

# 74LVT32373 • 74LVTH32373 Low Voltage 32-Bit Transparent Latch with 3-STATE Outputs (Preliminary)

## **General Description**

The LVT32373 and LVTH32373 contain thirty-two non-inverting latches with 3-STATE outputs and are intended for bus oriented applications. The device is byte controlled. The flip-flops appear transparent to the data when the Latch Enable (LE) is HIGH. When LE is LOW, the data that meets the setup time is latched. Data appears on the bus when the Output Enable ( $\overline{\text{OE}}$ ) is LOW. When  $\overline{\text{OE}}$  is HIGH, the outputs are in a high impedance state.

The LVTH32373 data inputs include bushold, eliminating the need for external pull-up resistors to hold unused inputs.

These latches are designed for low-voltage (3.3V)  $V_{CC}$  applications, but with the capability to provide a TTL interface to a 5V environment. The LVT32373 and LVTH32373 are fabricated with an advanced BiCMOS technology to achieve high speed operation similar to 5V ABT while maintaining a low power dissipation.

### **Features**

- $\blacksquare$  Input and output interface capability to systems at 5V  $V_{CC}$

- Bushold data inputs eliminate the need for external pull-up resistors to hold unused inputs (74LVTH32373), also available without bushold feature (74LVT32373)

- Live insertion/extraction permitted

- Power Up/Down high impedance provides glitch-free bus loading

- Outputs source/sink -32 mA/+64 mA

- ESD performance:

Human-body model > 2000V Machine model > 200V Charged-device model > 1000V

■ Packaged in plastic Fine-Pitch Ball Grid Array (FBGA) (Preliminary)

## **Ordering Code:**

| Order Number              | Package Number | Package Description                                                                 |

|---------------------------|----------------|-------------------------------------------------------------------------------------|

| 74LVT32373GX<br>(Note 1)  |                | 96-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide [TAPE and REEL] |

| 74LVTH32373GX<br>(Note 1) |                | 96-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide [TAPE and REEL] |

Note 1: BGA package available in Tape and Reel only.

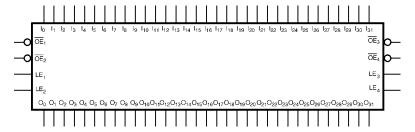

### Logic Symbol

# **Connection Diagram**

(Top Thru View)

# **Pin Descriptions**

| Pin Names                       | Description                      |

|---------------------------------|----------------------------------|

| $\overline{OE}_n$               | Output Enable Input (Active LOW) |

| LE <sub>n</sub>                 | Latch Enable Input               |

| I <sub>0</sub> –I <sub>31</sub> | Inputs                           |

| O <sub>0</sub> -O <sub>31</sub> | 3-STATE Outputs                  |

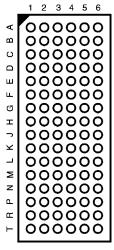

## **FBGA Pin Assignments**

|   | 1               | 2               | 3                | 4                | 5               | 6               |

|---|-----------------|-----------------|------------------|------------------|-----------------|-----------------|

| Α | O <sub>1</sub>  | O <sub>0</sub>  | OE <sub>1</sub>  | LE <sub>1</sub>  | I <sub>0</sub>  | I <sub>1</sub>  |

| В | O <sub>3</sub>  | O <sub>2</sub>  | GND              | GND              | l <sub>2</sub>  | l <sub>3</sub>  |

| С | O <sub>5</sub>  | O <sub>4</sub>  | V <sub>CC1</sub> | V <sub>CC1</sub> | I <sub>4</sub>  | I <sub>5</sub>  |

| D | O <sub>7</sub>  | O <sub>6</sub>  | GND              | GND              | I <sub>6</sub>  | I <sub>7</sub>  |

| E | O <sub>9</sub>  | O <sub>8</sub>  | GND              | GND              | I <sub>8</sub>  | l <sub>9</sub>  |

| F | O <sub>11</sub> | O <sub>10</sub> | V <sub>CC1</sub> | V <sub>CC1</sub> | I <sub>10</sub> | I <sub>11</sub> |

| G | O <sub>13</sub> | O <sub>12</sub> | GND              | GND              | I <sub>12</sub> | I <sub>13</sub> |

| Н | O <sub>14</sub> | O <sub>15</sub> | OE <sub>2</sub>  | LE <sub>2</sub>  | I <sub>15</sub> | I <sub>14</sub> |

| J | O <sub>17</sub> | O <sub>16</sub> | OE <sub>3</sub>  | LE <sub>3</sub>  | I <sub>16</sub> | I <sub>17</sub> |

| K | O <sub>19</sub> | O <sub>18</sub> | GND              | GND              | I <sub>18</sub> | I <sub>19</sub> |

| L | O <sub>21</sub> | O <sub>20</sub> | V <sub>CC2</sub> | V <sub>CC2</sub> | I <sub>20</sub> | l <sub>21</sub> |

| M | O <sub>23</sub> | O <sub>22</sub> | GND              | GND              | l <sub>22</sub> | l <sub>23</sub> |

| N | O <sub>25</sub> | O <sub>24</sub> | GND              | GND              | l <sub>24</sub> | l <sub>25</sub> |

| Р | O <sub>27</sub> | O <sub>26</sub> | $V_{CC2}$        | V <sub>CC2</sub> | I <sub>26</sub> | l <sub>27</sub> |

| R | O <sub>29</sub> | O <sub>28</sub> | GND              | GND              | I <sub>28</sub> | l <sub>29</sub> |

| Т | O <sub>30</sub> | O <sub>31</sub> | ŌE <sub>4</sub>  | LE <sub>4</sub>  | I <sub>31</sub> | I <sub>30</sub> |

### **Truth Table**

|                 | Inputs          |                                  | Outputs                          |

|-----------------|-----------------|----------------------------------|----------------------------------|

| CP <sub>1</sub> | OE <sub>1</sub> | I <sub>0</sub> –I <sub>7</sub>   | O <sub>0</sub> -O <sub>7</sub>   |

| Х               | Н               | X                                | Z                                |

| Н               | L               | L                                | L                                |

| Н               | L               | Н                                | Н                                |

| L               | L               | X                                | $O_0$                            |

|                 | Inputs          |                                  | Outputs                          |

| CP <sub>3</sub> | OE <sub>3</sub> | I <sub>16</sub> -I <sub>23</sub> | O <sub>16</sub> -O <sub>23</sub> |

| Х               | Н               | Х                                | Z                                |

| Н               | L               | L                                | L                                |

| Н               | L               | Н                                | Н                                |

| L               | L               | X                                | O <sub>0</sub>                   |

|                 | Inputs                    |                                  | Outputs                                     |

|-----------------|---------------------------|----------------------------------|---------------------------------------------|

| CP <sub>2</sub> | OE <sub>2</sub>           | I <sub>8</sub> -I <sub>15</sub>  | O <sub>8</sub> -O <sub>15</sub>             |

| Х               | Н                         | Х                                | Z                                           |

| Н               | L                         | L                                | L                                           |

| Н               | L                         | Н                                | Н                                           |

| L               | L                         | Χ                                | O <sub>0</sub>                              |

|                 |                           |                                  |                                             |

|                 | Inputs                    |                                  | Outputs                                     |

| CP <sub>4</sub> | Inputs<br>OE <sub>4</sub> | I <sub>24</sub> –I <sub>31</sub> | Outputs<br>O <sub>24</sub> –O <sub>31</sub> |

| CP <sub>4</sub> |                           | I <sub>24</sub> –I <sub>31</sub> | -                                           |

|                 | OE <sub>4</sub>           |                                  | O <sub>24</sub> -O <sub>31</sub>            |

| Х               | OE <sub>4</sub>           | Х                                | O <sub>24</sub> -O <sub>31</sub>            |

$H = HIGH \ Voltage \ Level \qquad X = Immaterial \qquad Z = HIGH \ Impedance \qquad O_o = Previous \ O_o \ prior \ to \ HIGH-to-LOW \ transition \ of \ LE \ Immaterial \ Description \$

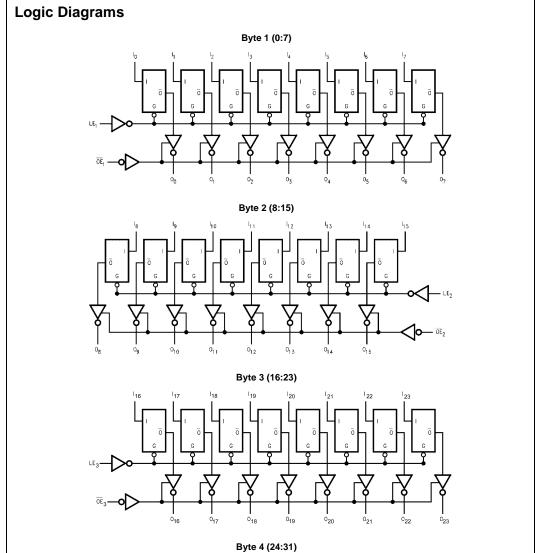

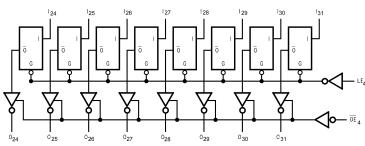

### **Functional Description**

The LVT32373 and LVTH32373 contain thirty-two D-type latches with 3-STATE standard outputs. The device is byte controlled with each byte functioning identically, but independent of the other. Control pins can be shorted together to obtain full 32-bit operation. The following description applies to each byte. When the Latch Enable (LE<sub>n</sub>) input is HIGH, data on the D<sub>n</sub> enters the latches. In this condition the latches are transparent, i.e, a latch output will change states each time its D input changes. When LE<sub>n</sub> is LOW, the latches store information that was present on the D inputs a setup time preceding the HIGH-to-LOW transition of LE<sub>n</sub>. The 3-STATE standard outputs are controlled by the Output Enable ( $\overline{OE}_n$ ) input. When  $\overline{OE}_n$  is LOW, the standard outputs are in the 2-state mode. When  $\overline{OE}_n$  is HIGH, the standard outputs are in the high impedance mode but this does not interfere with entering new data into the latches.

$V_{\mbox{\footnotesize{CC1}}}$  is associated with Bytes 1 and 2.

$\rm V_{\rm CC2}$  is associated with Bytes 3 and 4.

Note: Please note that these diagrams are provided only for the understanding of logic operations and should not be used to estimate propagation delays.

| Symbol | Parameter                        | Value        | Conditions                                            | Units |

|--------|----------------------------------|--------------|-------------------------------------------------------|-------|

| СС     | Supply Voltage                   | -0.5 to +4.6 |                                                       | V     |

| I      | DC Input Voltage                 | -0.5 to +7.0 |                                                       | V     |

| о́     | DC Output Voltage                | -0.5 to +7.0 | Output in 3-STATE                                     | V     |

|        |                                  | -0.5 to +7.0 | Output in HIGH or LOW State (Note 3)                  | V     |

| K      | DC Input Diode Current           | -50          | V <sub>I</sub> < GND                                  | mA    |

| Ж      | DC Output Diode Current          | -50          | V <sub>O</sub> < GND                                  | mΑ    |

| )      | DC Output Current                | 64           | V <sub>O</sub> > V <sub>CC</sub> Output at HIGH State | mA    |

|        |                                  | 128          | V <sub>O</sub> > V <sub>CC</sub> Output at LOW State  | IIIA  |

| C      | DC Supply Current per Supply Pin | ±64          |                                                       | mA    |

| SND    | DC Ground Current per Ground Pin | ±128         |                                                       | mA    |

| STG    | Storage Temperature              | -65 to +150  |                                                       | °C    |

# **Recommended Operating Conditions**

| Symbol          | Parameter                                               | Min | Max | Units |

|-----------------|---------------------------------------------------------|-----|-----|-------|

| V <sub>CC</sub> | Supply Voltage                                          | 2.7 | 3.6 | V     |

| VI              | Input Voltage                                           | 0   | 5.5 | V     |

| I <sub>OH</sub> | HIGH Level Output Current                               |     | -32 | mA    |

| I <sub>OL</sub> | LOW Level Output Current                                |     | 64  | mA    |

| T <sub>A</sub>  | Free-Air Operating Temperature                          | -40 | 85  | °C    |

| Δt/ΔV           | Input Edge Rate, $V_{IN} = 0.8V-2.0V$ , $V_{CC} = 3.0V$ | 0   | 10  | ns/V  |

Note 2: Absolute Maximum continuous ratings are those values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute maximum rated conditions is not implied.

Note 3: Io Absolute Maximum Rating must be observed.

## **DC Electrical Characteristics**

| Symbol               | Parameter                      |              | V <sub>CC</sub> | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      | Units | Conditions                            |  |

|----------------------|--------------------------------|--------------|-----------------|-----------------------------------------------|------|-------|---------------------------------------|--|

| Зупівої              | Farameter                      | raiameter    |                 | Min                                           | Max  | Units | Conditions                            |  |

| V <sub>IK</sub>      | Input Clamp Diode Voltage      |              | 2.7             |                                               | -1.2 | V     | $I_I = -18 \text{ mA}$                |  |

| V <sub>IH</sub>      | Input HIGH Voltage             |              | 2.7-3.6         | 2.0                                           |      | V     | $V_0 \le 0.1V$ or                     |  |

| V <sub>IL</sub>      | Input LOW Voltage              |              | 2.7-3.6         |                                               | 0.8  | V     | $V_O \ge V_{CC} - 0.1V$               |  |

| V <sub>OH</sub>      | Output HIGH Voltage            |              | 2.7-3.6         | V <sub>CC</sub> - 0.2                         |      |       | $I_{OH} = -100 \mu A$                 |  |

|                      |                                |              | 2.7             | 2.4                                           |      | V     | $I_{OH} = -8 \text{ mA}$              |  |

|                      |                                |              | 3.0             | 2.0                                           |      |       | I <sub>OH</sub> = -32 mA              |  |

| V <sub>OL</sub>      | Output LOW Voltage             |              | 2.7             |                                               | 0.2  |       | $I_{OL} = 100 \mu A$                  |  |

|                      |                                |              | 2.7             |                                               | 0.5  |       | I <sub>OL</sub> = 24 mA               |  |

|                      |                                |              | 3.0             |                                               | 0.4  | V     | I <sub>OL</sub> = 16 mA               |  |

|                      |                                |              | 3.0             |                                               | 0.5  |       | I <sub>OL</sub> = 32 mA               |  |

|                      |                                |              | 3.0             |                                               | 0.55 |       | I <sub>OL</sub> = 64 mA               |  |

| I <sub>I(HOLD)</sub> | Bushold Input Minimum Drive    |              | 3.0             | 75                                            |      | μΑ    | $V_{I} = 0.8V$                        |  |

| (Note 4)             |                                |              | 3.0             | -75                                           |      | μΛ    | V <sub>I</sub> = 2.0V                 |  |

| I <sub>I(OD)</sub>   | Bushold Input Over-Drive       |              | 3.0             | 500                                           |      | μА    | (Note 5)                              |  |

| (Note 4)             | Current to Change State        |              | 3.0             | -500                                          |      | μΛ    | (Note 6)                              |  |

| II                   | Input Current                  |              | 3.6             |                                               | 10   |       | V <sub>I</sub> = 5.5V                 |  |

|                      |                                | Control Pins | 3.6             |                                               | ±1   | μА    | $V_I = 0V \text{ or } V_{CC}$         |  |

|                      |                                | Data Pins    | 3.6             |                                               | -5   | μΑ    | $V_I = 0V$                            |  |

|                      |                                | Data i ilis  | 5.0             |                                               | 1    |       | $V_I = V_{CC}$                        |  |

| I <sub>OFF</sub>     | Power Off Leakage Current      |              | 0               |                                               | ±100 | μΑ    | $0V \le V_I \text{ or } V_O \le 5.5V$ |  |

| I <sub>PU/PD</sub>   | Power up/down 3-STATE          |              | 0-1.5V          |                                               | ±100 | μA    | $V_0 = 0.5V \text{ to } 3.0V$         |  |

|                      | Output Current                 |              | 0-1.50          |                                               | ±100 | μΛ    | $V_I = GND \text{ or } V_{CC}$        |  |

| l <sub>OZL</sub>     | 3-STATE Output Leakage Current |              | 3.6             |                                               | -5   | μΑ    | V <sub>O</sub> = 0.5V                 |  |

| l <sub>OZH</sub>     | 3-STATE Output Leakage Current |              | 3.6             |                                               | 5    | μΑ    | $V_0 = 3.0V$                          |  |

| I <sub>OZH</sub> +   | 3-STATE Output Leakage Current |              | 3.6             |                                               | 10   | μΑ    | $V_{CC} < V_O \le 5.5V$               |  |

# DC Electrical Characteristics (Continued)

| Symbol             | Parameter                        |                                         | V <sub>CC</sub> | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      | Units | Conditions                             |  |

|--------------------|----------------------------------|-----------------------------------------|-----------------|-----------------------------------------------|------|-------|----------------------------------------|--|

| Cymbol             |                                  |                                         | (V)             | Min                                           | Max  | Units | Conditions                             |  |

| I <sub>CCH</sub>   | Power Supply Current             | (V <sub>CC1</sub> or V <sub>CC2</sub> ) | 3.6             |                                               | 0.19 | mA    | Outputs HIGH                           |  |

| I <sub>CCL</sub>   | Power Supply Current             | (V <sub>CC1</sub> or V <sub>CC2</sub> ) | 3.6             |                                               | 5    | mA    | Outputs LOW                            |  |

| I <sub>CCZ</sub>   | Power Supply Current             | (V <sub>CC1</sub> or V <sub>CC2</sub> ) | 3.6             |                                               | 0.19 | mA    | Outputs Disabled                       |  |

| I <sub>CCZ</sub> + | Power Supply Current             | (V <sub>CC1</sub> or V <sub>CC2</sub> ) | 3.6             |                                               | 0.19 | mA    | $V_{CC} \le V_O \le 5.5V$ ,            |  |

|                    |                                  |                                         |                 |                                               |      |       | Outputs Disabled                       |  |

| $\Delta I_{CC}$    | Increase in Power Supply Current | (V <sub>CC1</sub> or V <sub>CC2</sub> ) | 3.6             |                                               | 0.2  | mA    | One Input at V <sub>CC</sub> – 0.6V    |  |

|                    | (Note 7)                         |                                         |                 |                                               |      |       | Other Inputs at V <sub>CC</sub> or GND |  |

Note 4: Applies to bushold versions only (74LVTH32373).

Note 5: An external driver must source at least the specified current to switch from LOW-to-HIGH.

Note 6: An external driver must sink at least the specified current to switch from HIGH-to-LOW.

Note 7: This is the increase in supply current for each input that is at the specified voltage level rather than  $V_{CC}$  or GND.

# **Dynamic Switching Characteristics** (Note 8)

| Symbol           | ol Parameter                                 |     | Parameter V <sub>CC</sub> T <sub>A</sub> = 25°C |      | Units |       | Conditions                                                                                      |  |

|------------------|----------------------------------------------|-----|-------------------------------------------------|------|-------|-------|-------------------------------------------------------------------------------------------------|--|

| Oymboi           | i arameter                                   | (V) | Min Typ Max                                     |      | Max   | Omits | $\textbf{C}_{\textbf{L}} = \textbf{50}~\text{pF},~\textbf{R}_{\textbf{L}} = \textbf{500}\Omega$ |  |

| V <sub>OLP</sub> | Quiet Output Maximum Dynamic V <sub>OL</sub> | 3.3 |                                                 | 0.8  |       | V     | (Note 9)                                                                                        |  |

| V <sub>OLV</sub> | Quiet Output Minimum Dynamic V <sub>OL</sub> | 3.3 |                                                 | -0.8 |       | V     | (Note 9)                                                                                        |  |

Note 8: Characterized in SSOP package. Guaranteed parameter, but not tested.

Note 9: Max number of outputs defined as (n). n-1 data inputs are driven 0V to 3V. Output under test held LOW.

### **AC Electrical Characteristics**

| Symbol           |                                  | T <sub>A</sub> =     |           |                 |       |     |

|------------------|----------------------------------|----------------------|-----------|-----------------|-------|-----|

|                  | Parameter                        | V <sub>CC</sub> = 3. | 3V ± 0.3V | V <sub>CC</sub> | Units |     |

|                  |                                  | Min                  | Max       | Min             | Max   | 1   |

| t <sub>PHL</sub> | Propagation Delay                | 1.5                  | 3.9       | 1.5             | 4.3   | ns  |

| t <sub>PLH</sub> | $D_n$ to $O_n$                   | 1.5                  | 3.8       | 1.5             | 4.2   | 115 |

| t <sub>PHL</sub> | Propagation Delay                | 1.9                  | 4.2       | 1.9             | 4.4   | no  |

| t <sub>PLH</sub> | LE to O <sub>n</sub>             | 1.6                  | 4.3       | 1.6             | 4.8   | ns  |

| t <sub>PZL</sub> | Output Enable Time               | 1.3                  | 4.3       | 1.3             | 4.9   | ns  |

| t <sub>PZH</sub> |                                  | 1.0                  | 4.3       | 1.0             | 5.1   | 115 |

| t <sub>PLZ</sub> | Output Disable Time              | 1.5                  | 4.7       | 1.5             | 4.8   |     |

| t <sub>PHZ</sub> |                                  | 2.0                  | 5.0       | 2.0             | 5.4   | ns  |

| t <sub>S</sub>   | Setup Time, D <sub>n</sub> to LE | 1.0                  |           | 0.8             |       | ns  |

| t <sub>H</sub>   | Hold Time, D <sub>n</sub> to LE  | 1.0                  |           | 1.1             |       | ns  |

| t <sub>W</sub>   | LE Pulse Width                   | 3.0                  |           | 3.0             |       | ns  |

# Capacitance (Note 10)

| Symbol           | Parameter          | Conditions                                                     | Typical | Units |

|------------------|--------------------|----------------------------------------------------------------|---------|-------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>CC</sub> = Open, V <sub>I</sub> = 0V or V <sub>CC</sub> | 4       | pF    |

| C <sub>OUT</sub> | Output Capacitance | $V_{CC} = 3.0V$ , $V_{O} = 0V$ or $V_{CC}$                     | 8       | pF    |

Note 10: Capacitance is measured at frequency f = 1 MHz, per MIL-STD-883, Method 3012.

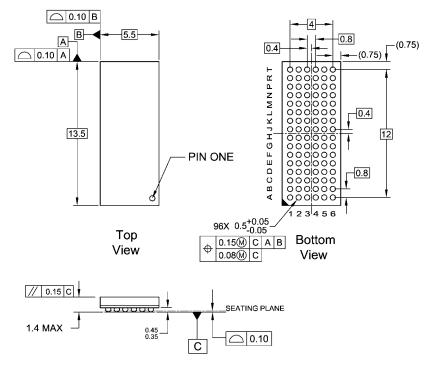

## Physical Dimensions inches (millimeters) unless otherwise noted

### NOTES:

- A. THIS PACKAGE CONFORMS TO JEDEC M0-205

- B. ALL DIMENSIONS IN MILLIMETERS

- C. LAND PATTERN RECOMMENDATION: NSMD (Non Solder Mask Defined)

.35MM DIA PADS WITH A SOLDERMASK OPENING OF .45MM CONCENTRIC TO PADS

D. DRAWING CONFORMS TO ASME Y14.5M-1994

BGA96ArevE

96-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide Package Number BGA96A **Preliminary**

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.