National Semiconductor

## 74LVT16652 3.3V ABT 16-Bit Transceiver/Register with TRI-STATE® Outputs

## **General Description**

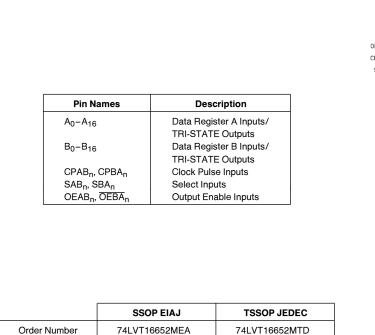

The LVT16652 consists of sixteen bus transceiver circuits with D-type flip-flops, and control circuitry arranged for multiplexed transmission of data directly from the input bus or from the internal registers. Each byte has separate control inputs which can be shorted together for full 16-bit operation. Data on the A or B bus will be clocked into the registers as the appropriate clock pin goes to HIGH logic level. Output Enable pins (OEAB, OEBA) are provided to control the transceiver function.

The transceivers are designed for low-voltage (3.3V)  $V_{CC}$  applications, but with the capability to provide a TTL interface to a 5V environment. The LVT16652 is fabricated with an advanced BiCMOS technology to achieve high speed operation similar to 5V ABT while maintaining a low power dissipation.

## Features

$\blacksquare$  Input and output interface capability to systems at 5V  $V_{CC}$

**ADVANCE INFORMATION**

October 1995

- Bus-Hold data inputs eliminate the need for external pull-up resistors to hold unused inputs

- Live insertion/extraction permitted

- Power Up/Down high impedance provides glitch-free bus loading

- Outputs source/sink -32 mA/+64 mA

- Available in SSOP and TSSOP

- Functionally compatible with the 74 series 16652

- Latch-up performance exceeds 500 mA

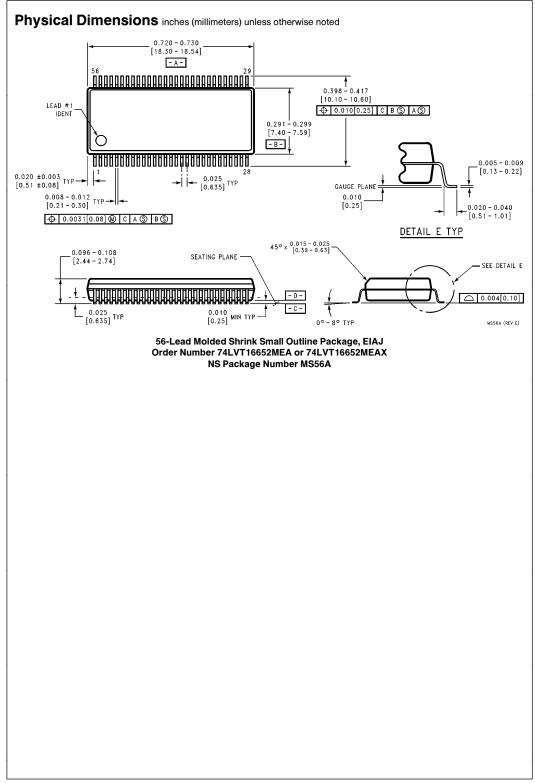

74LVT16652MEAX

MS56A

| -    |        | -              |      |

|------|--------|----------------|------|

| (`on | nectio | n Dia          | aram |

| GUI  |        | JI I 1 I C I C |      |

|                     | n Assignme<br>SOP and TS |    |                     |

|---------------------|--------------------------|----|---------------------|

| 1                   |                          |    | 1                   |

| OEAB1 -             |                          | 56 | OEBA,               |

| СРАВ                | 2                        | 55 | - СРВА              |

| SAB1 -              | 3                        | 54 | - SBA1              |

| GND -               | 4                        | 53 | - GND               |

| A0 —                | 5                        | 52 | — в <sub>о</sub>    |

| A1 —                | 6                        | 51 | — B <sub>1</sub>    |

| v <sub>cc</sub> —   | 7                        | 50 | — v <sub>cc</sub>   |

| A <sub>2</sub> —    | 8                        | 49 | — B <sub>2</sub>    |

| Α3 —                | 9                        | 48 | — B <sub>3</sub>    |

| Α4 -                | 10                       | 47 | — B <sub>4</sub>    |

| GND —               | 11                       | 46 | - GND               |

| А <sub>5</sub> —    | 12                       | 45 | — в <sub>5</sub>    |

| A <sub>6</sub> —    | 13                       | 44 | — в <sub>6</sub>    |

| A7 —                | 14                       | 43 | — B <sub>7</sub>    |

| А <sub>8</sub> —    | 15                       | 42 | — в <sub>8</sub>    |

| Ag —                | 16                       | 41 | — в <sub>9</sub>    |

| A <sub>10</sub> —   | 17                       | 40 | — в <sub>10</sub>   |

| GND —               | 18                       | 39 | - GND               |

| A <sub>11</sub> —   | 19                       | 38 | — B <sub>1 1</sub>  |

| A <sub>12</sub> —   | 20                       | 37 | — B <sub>1 2</sub>  |

| A <sub>13</sub> —   | 21                       | 36 | — B <sub>13</sub>   |

| v <sub>cc</sub> –   | 22                       | 35 | – v <sub>cc</sub>   |

| A <sub>1.4</sub> —  | 23                       | 34 | — B <sub>14</sub>   |

| A <sub>15</sub> —   | 24                       | 33 | — B <sub>15</sub>   |

| GND —               | 25                       | 32 | - GND               |

| sab <sub>2</sub> —  | 26                       | 31 | - SBA2              |

| срав <sub>2</sub> — | 27                       | 30 | - CPBA <sub>2</sub> |

| 0EAB <sub>2</sub> — | 28                       | 29 | - OEBA2             |

|                     |                          |    | TL/F/12024-1        |

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

© 1996 National Semiconductor Corporation TL/F/12024

NS Package

Number

RRD-B30M17/Printed in U. S. A.

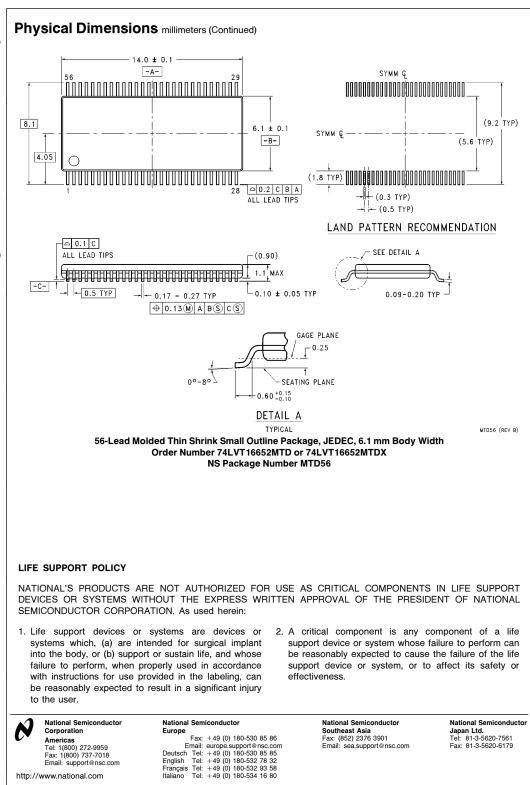

74LVT16652MTDX

MTD56

http://www.national.com

'4LVT16652 3.3V ABT 16-Bit Transceiver/Register with TRI-STATE Outputs

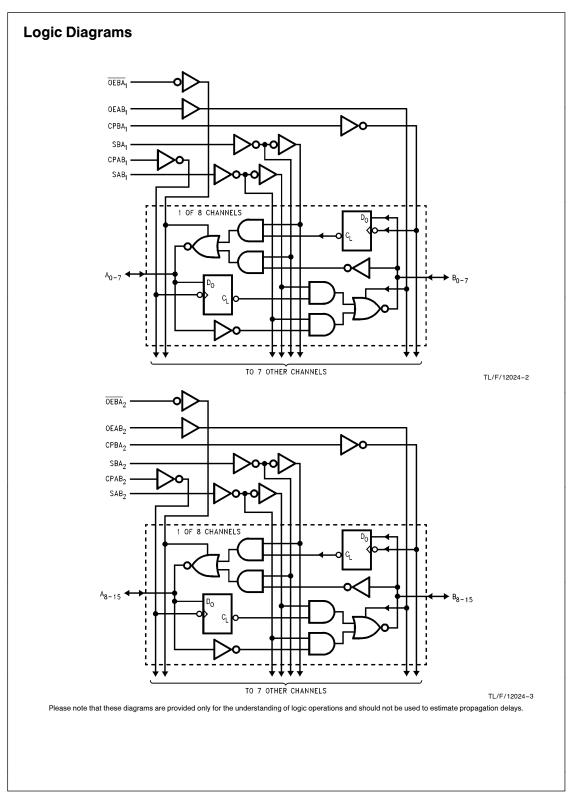

## **Functional Description**

In the transceiver mode, data present at the HIGH impedance port may be stored in either the A or B register or both. The select (SAB<sub>n</sub>, SBA<sub>n</sub>) controls can multiplex stored and real-time.

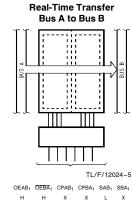

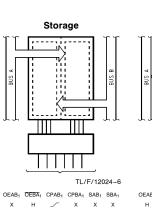

The examples in *Figure 1* demonstrate the four fundamental bus-management functions that can be performed with the LVT16652.

Data on the A or B data bus, or both can be stored in the internal D flip-flop by LOW to HIGH transitions at the appro-

Real-Time Transfer Bus B to Bus A

OEAB1 OEBA1 CPAB1 CPBA1 SAB1 SBA1

L X X X L

Tweets Table

1

х

x x

х \_

х

∟ н FIGURE 1

L

priate Clock Inputs (CPABn, CPBAn) regardless of the Se-

lect or Output Enable Inputs. When SAB and SBA are in the real time transfer mode, it is also possible to store data

without using the internal D flip-flops by simultaneously en-

abling  $\mathsf{OEAB}_n$  and  $\overline{\mathsf{OEBA}}_n.$  In this configuration each Output

reinforces its Input. Thus when all other data sources to the

two sets of bus lines are in a HIGH impedance state, each

set of bus lines will remain at its last state.

Transfer Storage

Data to A or B

OEAB1 OEBA1 CPAB1 CPBA1 SAB1 SBA1 H L HorL HorL H H

| Irutr             | Table             | (Note)            |                   |      |                  |                                    |                                    |                                                     |           |

|-------------------|-------------------|-------------------|-------------------|------|------------------|------------------------------------|------------------------------------|-----------------------------------------------------|-----------|

| Inputs            |                   |                   |                   |      | Inputs/Outputs   |                                    | Operating Mode                     |                                                     |           |

| OEAB <sub>1</sub> | OEBA <sub>1</sub> | CPAB <sub>1</sub> | CPBA <sub>1</sub> | SAB1 | SBA <sub>1</sub> | A <sub>0</sub> thru A <sub>7</sub> | B <sub>0</sub> thru B <sub>7</sub> |                                                     |           |

| L                 | Н                 | H or L            | H or L            | x    | X                | Input                              | Input Isolation                    | Isolation                                           | Isolation |

| L                 | н                 |                   | <i>_</i>          | x    | x                |                                    | Store A and B Data                 |                                                     |           |

| х                 | Н                 |                   | H or L            | х    | x                | Input                              | Not Specified                      | Store A, Hold B                                     |           |

| н                 | н                 |                   | <u>~</u>          | x    | x                | Input                              | Output                             | Store A in Both Registers                           |           |

| L                 | Х                 | H or L            | <u> </u>          | х    | х                | Not Specified                      | Input                              | Hold A, Store B                                     |           |

| L                 | L                 |                   | <u>~</u>          | x    | x                | Output                             | Input                              | Store B in Both Registers                           |           |

| L                 | L                 | х                 | х                 | х    | L                | Output                             | Input                              | Real-Time B Data to A Bus                           |           |

| L                 | L                 | x                 | H or L            | x    | н                | Culput                             | mpar                               | Store B Data to A Bus                               |           |

| Н                 | н                 | x                 | х                 | L    | x                | Input                              | Output                             | Real-Time A Data to B Bus                           |           |

| н                 | Н                 | H or L            | х                 | н    | х                | mpat                               | Culput                             | Stored A Data to B Bus                              |           |

| н                 | L                 | H or L            | H or L            | н    | н                | Output                             | Output                             | Stored A Data to B Bus an<br>Stored B Data to A Bus |           |

H = HIGH Voltage Level L = LOW Voltage Level X = Immaterial  $\checkmark$  = LOW to HIGH Clock Transition

Note: The data output functions may be enabled or disabled by various signals at OEAB or OEBA inputs. Data input functions are always enabled, i.e., data at the bus pins will be stored on every LOW to HIGH transition on the clock inputs. This also applies to data I/O (A and B: 8–15) and #2 control pins.

| Temperature Range Family ————<br>74LVT = Commercial                                                           | <u>74LVT</u> | <u>16652</u> | MEA  | X<br>Special Variations<br>"X" = Tape and Re |

|---------------------------------------------------------------------------------------------------------------|--------------|--------------|------|----------------------------------------------|

| Device Type                                                                                                   |              |              |      | "" = Rail/Tube                               |

|                                                                                                               |              |              |      |                                              |

| Package Code<br>MEA = Molded Shrink Small Outline Pac<br>MTD = Molded Thin Shrink Small Outline<br>Body Width |              | EDEC, 4.     | 4 mm |                                              |

|                                                                                                               |              |              |      |                                              |

|                                                                                                               |              |              |      |                                              |

|                                                                                                               |              |              |      |                                              |

|                                                                                                               |              |              |      |                                              |

|                                                                                                               |              |              |      |                                              |

|                                                                                                               |              |              |      |                                              |

|                                                                                                               |              |              |      |                                              |

|                                                                                                               |              |              |      |                                              |

|                                                                                                               |              |              |      |                                              |

|                                                                                                               |              |              |      |                                              |

|                                                                                                               |              |              |      |                                              |

\_

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

This datasheet has been downloaded from:

www.DatasheetCatalog.com

Datasheets for electronic components.