# **CXG1092N**

# **SP5T GSM Triple-Band Antenna Switch**

#### Description

The CXG1092N is a high power antenna MMIC switch for use in triple-band GSM handsets.

One antenna can be routed to either of the 2 Tx or 3 Rx ports.

#### **Features**

- 4 CMOS compatible control lines

- Standby control

- 34.5dBm power handling at 5.0V (GSM900)

- Low second harmonic < -36dBm at 34.5dBm

- Small package size: 20-pin SSOP (6.4 × 5.0 × 1.25mm)

#### **Applications**

Triple-band handsets using combinations of GSM900/DCS1800/PCS1900 and DECT

#### Structure

GaAs J-FET MMIC (The Sony JFET process is used for low insertion loss.)

#### Absolute Maximum Ratings (Ta = 25°C)

| <ul> <li>Bias voltage</li> </ul>        | Vdd  | 7           | V  |

|-----------------------------------------|------|-------------|----|

| <ul> <li>Control voltage</li> </ul>     | VctI | 5           | V  |

| Operating temperature                   | Topr | -35 to +85  | °C |

| <ul> <li>Storage temperature</li> </ul> | Tstg | -65 to +150 | °C |

#### Note on Handling

GaAs MMICs are ESD sensitive devices. Special handling precautions are required.

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

## **Truth Table**

| On Pass                 | GSM900 | DCS1800 | PCS1900 | Rx ON | STDBY |

|-------------------------|--------|---------|---------|-------|-------|

| AntTx1 GSM900           | Н      | L       | L       | L     | Н     |

| AntTx2 GSM1800          | L      | Н       | L       | L     | Н     |

| AntRx1 GSM900/1800/1900 | Н      | L       | L       | Н     | Н     |

| AntRx2 GSM900/1800/1900 | L      | Н       | L       | Н     | Н     |

| AntRx3 GSM900/1800/1900 | L      | L       | Н       | Н     | Н     |

| OFF                     | _      | _       | _       | _     | L     |

# **CMOS logic values**

(Ta = 25°C)

| Logic | Min. | Тур. | Max. | Unit |

|-------|------|------|------|------|

| High  | 2.4  | 2.8  | 3.2  | V    |

| Low   | 0.0  |      | 0.4  | V    |

#### **Electrical Characteristics**

$(Ta = 25^{\circ}C)$

| Item                         | Symbol           | Port              | Condition            | Min. | Тур. | Max. | Unit |  |

|------------------------------|------------------|-------------------|----------------------|------|------|------|------|--|

| Insertion loss I             |                  | Ant-Tx1, Tx2      | *1                   |      | 0.6  | 0.9  | dB   |  |

|                              |                  |                   | *2                   |      | 0.7  | 1.0  | dB   |  |

|                              | IL               | Ant-Rx1, Rx2, Rx3 | *3                   |      | 0.6  | 0.9  | dB   |  |

|                              |                  |                   | *4                   |      | 0.85 | 1.1  | dB   |  |

|                              |                  |                   | *5                   |      | 0.9  | 1.15 | dB   |  |

|                              |                  | Ant-Tx1, Tx2      | *3                   | 15   |      |      | dB   |  |

| Isolation                    | 180              |                   | *4, *5               | 14   |      |      | dB   |  |

|                              | 130.             | Ant-Rx1, Rx2, Rx3 | *1                   | 18   |      |      | dB   |  |

|                              |                  |                   | *2                   | 17   |      |      | dB   |  |

| VSWR                         | VSWR             |                   |                      |      | 1.2  |      |      |  |

| Harmonics <sup>Note)</sup>   | 2fo              | Ant-Tx1, Tx2      | *1, *2               |      |      | -36  | dBm  |  |

| Trainfornes                  | 3fo              |                   | *1, *2               |      |      | -30  | dBm  |  |

| P <sub>1dB</sub> compression | P1dB compression | Ant-Tx1           |                      |      | 36   |      | dBm  |  |

| input power                  | P <sub>1dB</sub> | Ant-Tx2           |                      |      | 35.5 |      |      |  |

| Control current              | Ictl             |                   |                      |      |      | 170  | μA   |  |

| Supply current<br>Tx mode    | Ітх              |                   | STBY = H<br>TxON = L |      |      | 1    | mA   |  |

| Supply current<br>Rx mode    | lrx              |                   | STBY = H<br>RxON = H |      |      | 1    | mA   |  |

| Leakage current              | lıĸ              |                   | STBY = L             |      |      | 100  | μA   |  |

<sup>\*1</sup> Pin 1 = 34.5dBm, 880 to 915MHz, VDD = 5.0V (GSM Tx)

Note) Harmonics measured with Tx inputs harmonically matched.

Sony recommends the use of harmonic matching to ensure optimum device performance Application Note (1).

<sup>\*2</sup> Pin 2 = 32dBm, 1710 to 1910MHz, VDD = 5.0V (DCS & PCS Tx)

<sup>\*3</sup> Pin 3 = 10dBm, 925 to 960MHz (GSM Rx) \*4 Pin 4 = 10dBm, 1805 to 1880MHz (DCS Rx) \*5 Pin 5 = 10dBm, 1930 to 1990MHz (PCS Rx)

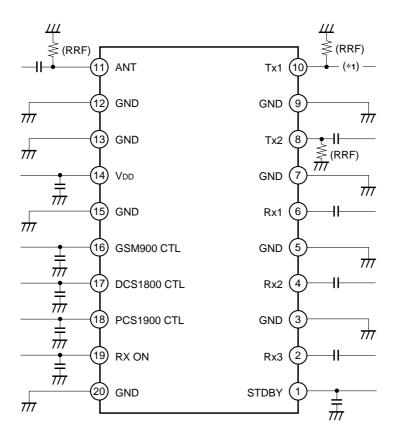

#### **Recommended Circuit**

## **Recommended PCB Layout**

- \* As indicated in the diagram AC coupling capacitors are necessary to the Ant, Tx1, Tx2, Rx1, Rx2 and Rx3 pins, and decoupling capacitors are necessary to the VDD, STDBY and CTL lines.

- \* The ground plane should be included under the device and all ground pins connected to this.

- \* RRF (200k $\Omega$ ) is used to stabilize the electrical characteristics at the high power signal input. These resistors are required to ensure correct operation of the switch.

- \*1 See Application Note (1).

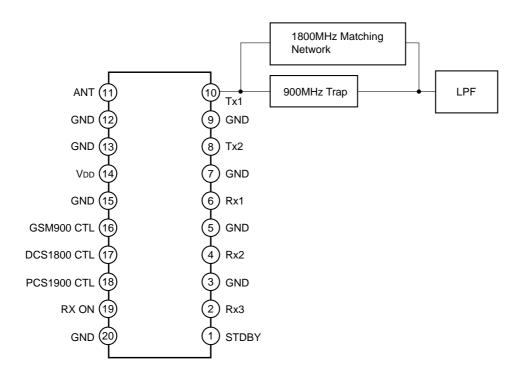

#### **Application Note (1)**

#### Impedance matching for harmonic minimization

To achieve the 2nd harmonic levels lower than -36dBm for GSM900

Design of 1.8GHz harmonic matching network and the 900MHz trap network is dependent on the board design and components.

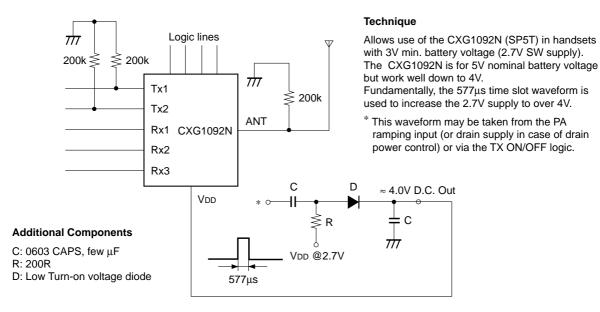

#### **Application Note (2)**

#### Operating the CXG1092 from a 3V supply

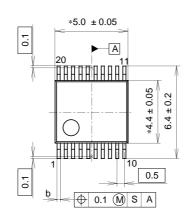

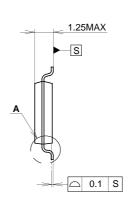

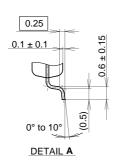

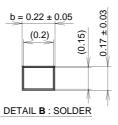

## Package Outline Unit: mm

## 20PIN SSOP(PLASTIC)

NOTE: Dimension "\*" does not include mold protrusion.

#### PACKAGE STRUCTURE

| SONY CODE  | SSOP-20P-L03   |

|------------|----------------|

| EIAJ CODE  | SSOP020-P-0044 |

| JEDEC CODE |                |

| PACKAGE MATERIAL | EPOXY RESIN                 |

|------------------|-----------------------------|

| LEAD TREATMENT   | SOLDER/PALLADIUM<br>PLATING |

| LEAD MATERIAL    | COPPER ALLOY                |

| PACKAGE MASS     | 0.1g                        |

# This datasheet has been downloaded from:

www. Data sheet Catalog.com

Datasheets for electronic components.