August 1996

# Comlinear CLC402 Low-Gain Op Amp with Fast 14-Bit Settling

# **General Description**

The CLC402 is an operational amplifier designed for low-gain applications ( $\pm 1$  to  $\pm 8$ ), requiring fast, accurate settling and superior DC accuracy. Settling to 0.0025% in 25ns (32ns guaranteed over temperature), the CLC402 is ideal as the input amplifier in high accuracy (up to 14-bits) A/D systems. Unlike most other high-speed op amps, the CLC402 is free of thermally induced tails in the settling response.

The CLC402 is an upgrade to and pin compatible with the industry standard CLC400. Constructed using a unique, proprietary design and an advanced complementary bipolar process, it offers performance far beyond ordinary monolithic op amps. In addition, unlike many other high-speed op amps, the CLC402 offers both high performance and stability without the need for compensation circuitry – even at a gain of +1.

Supporting the CLC402's excellent pulse performance are improved DC characteristics. The CLC402's input offset voltage is typically 0.5mV and is guaranteed to be less than 1.6mV at +25°C. The input offset voltage drift is typically only  $3\mu$ V/°C.

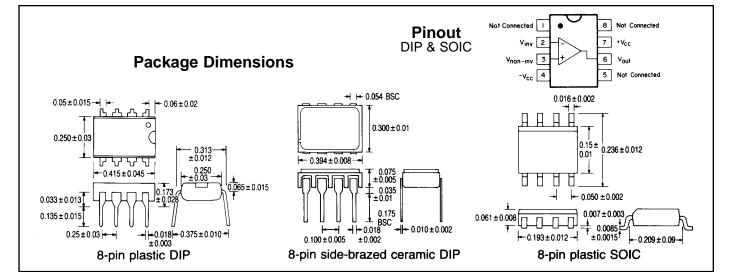

The CLC402 is available in several versions to meet a variety of requirements. A three-letter suffix determines the version:

| CLC402AJP - | 40°C to +85°C  | 8-pin plastic DIP              |

|-------------|----------------|--------------------------------|

| CLC402AJE - | 40°C to +85°C  | 8-pin plastic SOIC             |

| CLC402A8B - | 55°C to +125°C | 8-pin hermetic CERDIP,         |

|             |                | MIL-STD-833, Level B           |

| CLC402ALC - | 40°C to +85°C  | dice                           |

| CLC402AMC - | 55°C to +125°C | dice qualified to Method 5008, |

|             |                | MIL-STD-883, Level B           |

| CLC402AID - |                | 8-pin sidebrazed CERDIP        |

| CLC402A8D - | 55°C to +125°C | 8-pin sidebrazed CERDIP,       |

|             |                | MIL-STD-883, Level B           |

DESC SMD number: 5962-92033

# Features

- 0.0025% settling in 25ns (32ns max)

- 0.5mV input offset voltage, 3µV/°C drift

- ±1 to ±8 closed-loop gain range

- Low power, 150mW

- 0.01%/0.05° differential gain/phase

## **Applications**

- High-accuracy A/D systems (12-14 bits)

- High-accuracy D/A converters

- High-speed communications

- IF processors

- Video distribution

© 1996 National Semiconductor Corporation Printed in the U.S.A.

| CLC402 Electrica                                                                                                                                                                                                                                                     | al Characteristic                                                                                          | <b>S</b> (A <sub>v</sub> = +2                        | , $V_{cc} = \pm 5V$ ,                                         | R <sub>L</sub> = 100Ω                          | 2, R <sub>f</sub> = 250Ω                                       | ; unless spe                                                | cified)                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------|

| PARAMETER                                                                                                                                                                                                                                                            | CONDITIONS                                                                                                 | TYP                                                  | MAX                                                           | & MIN RAT                                      | TINGS                                                          | UNITS                                                       | SYMBOL                                                           |

| Ambient Temperature                                                                                                                                                                                                                                                  | CLC402A8/AL/AM                                                                                             | +25℃                                                 | _55℃                                                          | +25°C                                          | +125℃                                                          |                                                             |                                                                  |

| Ambient Temperature                                                                                                                                                                                                                                                  | CLC402AJ/AI                                                                                                | +25°C                                                | -40°C                                                         | +25°C                                          | + 85℃                                                          |                                                             |                                                                  |

| FREQUENCY DOMAIN PERF                                                                                                                                                                                                                                                | ORMANCE                                                                                                    |                                                      |                                                               |                                                |                                                                |                                                             |                                                                  |

| †-3dB bandwidth                                                                                                                                                                                                                                                      | V <sub>out</sub> <0.5V <sub>pp</sub><br>V <sub>out</sub> <5V <sub>pp</sub>                                 | 195<br><b>80</b>                                     | >120<br>>50                                                   | >130<br>>50                                    | >120<br>>50                                                    | MHz<br>MHz                                                  | SSBW<br>LSBW                                                     |

| gain flatness <sup>2</sup><br>† peaking<br>† peaking<br>† rolloff<br>linear phase deviation                                                                                                                                                                          | V <sub>out</sub> <0.5V <sub>pp</sub><br>DC to 25MHz<br>>25MHz<br>DC to 50MHz<br>DC to 50MHz<br>DC to 50MHz | 0<br>0<br>0.5<br>0.4                                 | <0.4<br><0.7<br><1.0<br><1.2                                  | <0.3<br><0.5<br><1.0<br><1.0                   | <0.4<br><0.7<br><1.0<br><1.2                                   | dB<br>dB<br>dB<br>°                                         | GFPL<br>GFPH<br>GFR<br>LPD                                       |

| TIME DOMAIN PERFORMAN<br>rise and fall time<br>settling time to $\pm 0.0025\%$<br>$\pm 0.01\%$<br>$\pm 0.1\%$<br>overshoot<br>slew rate                                                                                                                              | CE<br>0.5V step<br>5V step<br>2V step<br>2V step<br>2V step<br>0.5V step                                   | 2.0<br>5.0<br>25<br>18<br>10<br>0<br>800             | <2.9<br><8<br><32<br><25<br><15<br><10<br>>500                | <2.7<br><8<br><32<br><25<br><15<br><10<br>>500 | <2.9<br><8<br><32<br><25<br><15<br><10<br>>500                 | ns<br>ns<br>ns<br>ns<br>%<br>V/µs                           | TRS<br>TRL<br>TS14<br>TSP<br>TSS<br>OS<br>SR                     |

| DISTORTION AND NOISE PE<br>†2nd harmonic distortion<br>†3rd harmonic distortion<br>equivalent input noise<br>noise floor<br>integrated noise<br>differential gain <sup>1</sup><br>differential phase <sup>1</sup>                                                    | ERFORMANCE<br>2V <sub>pp</sub> , 20MHz<br>2V <sub>pp</sub> , 20MHz<br>>1MHz<br>1MHz to 150MHz              | -50<br>-60<br>-157<br>40<br>0.01<br>0.05             | <-38<br><-53<br><-155<br><49<br>                              | <-43<br><-53<br><-155<br><49<br>               | <-43<br><-50<br><-155<br><49<br>                               | dBc<br>dBc<br>dBm(1Hz)<br>μV<br>%<br>°                      | HD2<br>HD3<br>SNF<br>INV<br>DG<br>DP                             |

| STATIC, DC PERFORMANCE<br>*input offset voltage<br>average temperature coef<br>*input bias current<br>average temperature coef<br>*input bias current<br>average temperature coef<br>†power supply rejection ratio<br>common mode rejection ratio<br>*supply current | fficient<br>noninverting<br>fficient<br>inverting                                                          | 0.5<br>3<br>10<br>100<br>10<br>100<br>68<br>65<br>15 | <2.6<br><12<br><45<br><50<br><50<br><250<br>>55<br>>55<br><20 | <1.6<br>                                       | <2.8<br><12<br><35<br><100<br><40<br><100<br>>60<br>>60<br><20 | mV<br>μV/°C<br>μA<br>nA/°C<br>μA<br>nA/°C<br>dB<br>dB<br>mA | VIO<br>DVIO<br>IBN<br>DIBN<br>IBI<br>DIBI<br>PSRR<br>CMRR<br>ICC |

| MISCELLANEOUS PERFORM<br>noninverting input<br>output impedance<br>common mode input range<br>output voltage range<br>output current                                                                                                                                 | ANCE<br>resistance<br>capacitance<br>at DC<br>no load                                                      | 150<br>3.5<br>0.02<br>±3.0<br>±3.5V<br>±55           | >50<br><5.5<br><0.1<br>>±2.0<br>>±3.0<br>>±25                 | >85<br><5.5<br><0.1<br>>±2.5<br>>±3.2<br>>±45  | >85<br><5.5<br><0.1<br>>±2.5<br>>±3.2<br>>±45                  | kΩ<br>pF<br>Ω<br>V<br>V<br>mA                               | RIN<br>CIN<br>RO<br>CMIR<br>VO<br>IO                             |

output current $|| \pm 55 || > \pm 25 || > \pm 25 || > \pm 45 || > \pm 45 || mA || OMin/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.$

| Absolute Maximum Ratings                  |                                                                                                                             | Miscellaneous Ratings                                                                                                                                                     |  |  |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ±7V                                       | recommende                                                                                                                  | ed gain range: $\pm 1$ to $\pm 8$                                                                                                                                         |  |  |  |  |

| o ground,                                 |                                                                                                                             |                                                                                                                                                                           |  |  |  |  |

| but, maximum reliability will be obtained |                                                                                                                             |                                                                                                                                                                           |  |  |  |  |

| 70mA                                      | * AI, AJ                                                                                                                    | 100% tested at +25°C, sample at +85°C.                                                                                                                                    |  |  |  |  |

| $\pm V_{cc}$                              | † AJ                                                                                                                        | Sample tested at +25°C.                                                                                                                                                   |  |  |  |  |

| +175°Č                                    | † Al                                                                                                                        | 100% tested at +25°C.                                                                                                                                                     |  |  |  |  |

|                                           | * A8                                                                                                                        | 100% tested at +25°C, - 55°C, +125°C.                                                                                                                                     |  |  |  |  |

| – 40°C to +85°C                           | t A8                                                                                                                        | 100% tested at +25°C, sample at - 55°C, +125°C.                                                                                                                           |  |  |  |  |

| – 55°C to +125°C                          | * AL. AM                                                                                                                    | 100% wafer probe tested at +25°C to +25°C                                                                                                                                 |  |  |  |  |

| – 65°C to +150°C                          | min/max specifications.                                                                                                     |                                                                                                                                                                           |  |  |  |  |

| 10 sec                                    |                                                                                                                             |                                                                                                                                                                           |  |  |  |  |

|                                           | note 1:                                                                                                                     | Differential gain and phase measured at $A_v = +2V$ ,                                                                                                                     |  |  |  |  |

|                                           |                                                                                                                             | $R = 250\Omega$ , $R_L = 150\Omega$ , $1V_{pp}$ equivalent video signal                                                                                                   |  |  |  |  |

|                                           |                                                                                                                             | 0-100 IRE, 40 IRE <sub>pp</sub> , 0IRE = 0 volts, 75 $\Omega$ load                                                                                                        |  |  |  |  |

|                                           |                                                                                                                             | and 3.58 MHz.                                                                                                                                                             |  |  |  |  |

|                                           | note 2:                                                                                                                     | Gain flatness tests performed from 0.1MHz.                                                                                                                                |  |  |  |  |

|                                           |                                                                                                                             | F F                                                                                                                                                                       |  |  |  |  |

|                                           | ±7V<br>b ground,<br>btained<br>70mA<br>±V <sub>∞</sub><br>+175°C<br>- 40°C to +85°C<br>- 55°C to +125°C<br>- 65°C to +150°C | ±7V recommend<br>btained Notes:<br>70mA * AI, AJ<br>±V <sub>oc</sub> † AJ<br>+175°C † AI<br>* A8<br>− 40°C to +85°C † A8<br>− 55°C to +125°C * AL, AM<br>− 65°C to +150°C |  |  |  |  |

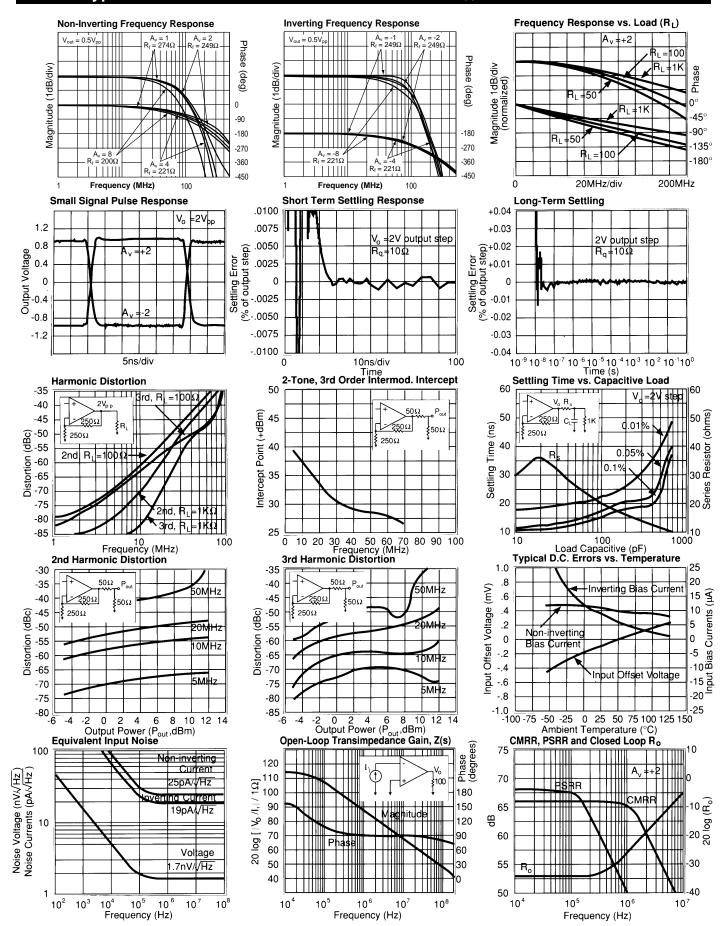

# CLC402 Typical Performance Characteristics (T<sub>A</sub> = 25°, A<sub>V</sub> = +2, V<sub>CC</sub> = ±5V, R<sub>L</sub> = 100Ω, Rf = 250Ω; unless specified)

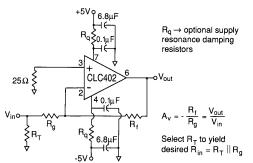

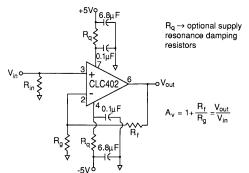

Figure 1: recommended inverting gain circuit

#### **Feedback Resistor**

The CLC402 achieves its excellent pulse response by using the current feedback topology pioneered by Comlinear Corporation. The loop gain for a current feedback op amp, and hence the frequency response, is predominantly set by the feedback resistor value. The CLC402 is optimized for use with a 250 $\Omega$  feedback resistor. Using lower values can lead to excessive ringing in the pulse response while a higher value will limit the bandwidth. Application Note OA-13 discusses this in detail along with occasions where a different R, might be advantageous.

#### **Optimizing Settling Time**

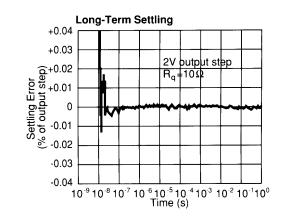

The CLC402 is capable of extremely fast pulse settling times to very fine scale accuracies (.0025% in 25ns typical). It is also virtually free of any measurable thermal tail effects as shown in the long-term settling time plot on the previous page. Careful attention to parasitic effects is critical to achieving this level of performance.

Generally, open any ground and/or power planes around the device while providing an adjacent ground plane for the  $0.1 \mu f$ ceramic decoupling caps. These caps should be very near the power pins. Connecting the ground return point for the electrolytic capacitors near the load ground point is also very useful. Similarly, for non-inverting applications, connecting R<sub>a</sub> to ground near the input terminating resistor ground connection will improve performance. These suggestions become particularly pertinent for fastest settling to lower than 0.1% accuracies.

Using Supply Resistors,  ${\rm R_q}$  Figures 1 and 2 show a series resistor in the supply leads between the electrolytic and ceramic capacitors. This optional resistor is intended to de-Q any self-resonance between those capacitors and the power supply trace inductance. Any large output voltage step into a significant load, either resistive or capacitive, will necessarily pull a current surge through the supply de-coupling capacitors. This can cause a very low level, high frequency ringing on the power supplies that may not be effectively rejected by the PSRR of the CLC402. This can, in turn, show up at the output as a ringing that will preclude high speed settling to very fine scale accuracies.

Adding  $R_{a}$  will increase the amplitude of this signal at the supplies but will lower the frequency content to where the CLC402's PSRR can effectively reject it. An  $R_{\alpha}$  of 5 to 10 $\Omega$ will yield excellent settling performance with minimal impact on other performance parameters.

#### **Driving Capacitive Loads**

Either parasitic or load capacitance directly on the output pin can guickly lead to unacceptable levels of ringing in the pulse response. Adding a series resistor, as shown in the plot of  $R_{\rm s}$  vs.  $C_{\rm L}$  on the previous page, will resolve this problem. Parasitic capacitances less than 2pF can be driven without the series resistor. See Application Note OA-15 for additional discussion.

#### **Distortion Performance**

The distortion plots show the harmonic distortions and 3rd order intermodulation intercepts under a variety of load, power, and frequency conditions. Generally, going to higher

Figure 2: recommended non-inverting gain circuit

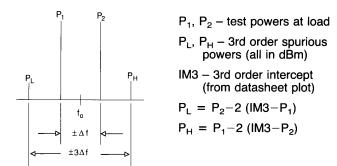

frequencies will degrade the distortion performance as the amplifier loop gain decreases. Further distortion improvements at low frequencies are observed when driving higher impedance loads. The 3rd order intermodulation intercept plot may be used to predict the 3rd order spurious levels given the power levels at the load for two closely spaced signal frequencies. Figure 3 shows the signal and spurious level definitions along with equations for predicting the spurious powers from the intercept value and the two signal powers.

#### Figure 3: 3rd order spurious calculations

#### **DC Accuracy and Noise**

The CLC402 offers an improved offset voltage over the comparable CLC400 low gain amplifier. The offset adjustment available on the CLC400 was therefore not included in this part. Figure 4 shows the output offset computational equation for the non-inverting configuration with an example using the typical bias current and offset specifications for  $A_v = +2$ .

**Output Offset**

$$V_{o} = \left( \pm I_{bn} R_{in} \pm V_{io} \right) \left( 1 + \frac{R_{f}}{R_{g}} \right) \pm I_{bi} R_{f}$$

Example computation for  $A_v = +2$ ,  $R_f = 250\Omega$

$V_0 = (\pm 10\mu A (50\Omega) \pm 0.5 mV) (2) \pm 10\mu A (250\Omega) = \pm 3.5 mV$

#### Figure 4: Output DC offset calculation

This low output offset voltage is a marked improvement over earlier very high speed amplifiers. Further improvement in the output offset voltage and drift is possible using the composite amplifiers described in Application Note OA-7.

The equivalent input noise plot shows that the CLC402 offers a low 1.7nV/VHz input noise voltage. A low non-inverting source impedance should be used for lowest noise performance due to the relatively high current noise at that input. See Application Note OA-12 for a full discussion of noise calculations for current feedback amplifiers.

#### **Printed Circuit Layout**

Evaluation PC boards (part number 730013 for through-hole and 730027 for SOIC) for the CLC402 are available. This board can be easily modified to include the R<sub>n</sub> resistors discussed above. Further layout suggestions may be found in Application Note OA-15.

This page intentionally left blank.

### **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at **1-800-272-9959** or fax **1-800-737-7018**.

#### Life Support Policy

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe Fax: (+49) 0-180-530 85 86 E-mail: europe.support.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Francais Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block Ocean Centre, 5 Canton Road Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor

Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.