# PLL frequency synthesizer for tuners **BU2616F**

BU2616F PLL frequency synthesizers work up through the FM band.

Featuring low power dissipation and highly sensitive built-in RF amps, they detect intermediate frequencies.

#### Applications

Tuners (Mini components, radio cassette players, radio equipment, etc.)

#### Features

- 1) Built-in high-speed prescaler can divide 130MHzVCO.

- Low current dissipation (during operation: 6mA PLL OFF: 1mA)

- In addition to the standard FM and AM, also offers the following 7 frequencies: 25kHz, 12.5kHz, 6.25kHz, 10kHz, 9kHz, 5kHz, and 1kHz.

- 4) SD (station detector) input circuit.

- 5) Intermediate frequency detection circuit

- 6) Charge pump output control circuit

- 7) Four output ports (Nch open drain).

- 8) Serial data input (CE, CK, DA)

## ●Absolute maximum ratings (Ta = 25°C)

| Parameter                | Symbol           | Limits                 | Unit | Conditions                               |

|--------------------------|------------------|------------------------|------|------------------------------------------|

| Power supply voltage     | VDD              | −0.3~ <del>+</del> 7.0 | ٧    | VDD                                      |

| Maximum input voltage 1  | VIN1             | <b>−0.3∼+7.0</b>       | ٧    | CE, CK, DA, SD                           |

| Maximum input voltage 2  | V <sub>IN2</sub> | -0.3~Vpp+0.3           | ٧    | XIN, FMIN, AMIN, IFIN                    |

| Maximum output voltage 1 | Vout1            | -0.3~+10.0             | ٧    | Po, P1, P2, P3, DO                       |

| Maximum output voltage 2 | VOUT2            | -0.3~Vpp+0.3           | ٧    | PD <sub>1</sub> , PD <sub>2</sub> , XOUT |

| Maximum output current   | Іоит             | 0~+3.0                 | mA   | Po, P1, P2, P3, DO                       |

| Power dissipation        | Pd               | 450*                   | mW   |                                          |

| Operating temperature    | Topr             | <b>−10</b> ~+75        | °    |                                          |

| Storage temperature      | Tstg             | -55~ <b>+12</b> 5      | °C   |                                          |

<sup>\*</sup> Reduced by 4.5mW for each increase in Ta of 1°C over 25°C.

#### ● Recommended operating conditions (Ta = 25°C)

| Parameter            | Symbol          | Limits  | Unit |

|----------------------|-----------------|---------|------|

| Power supply voltage | V <sub>DD</sub> | 4.0~6.0 | ٧    |

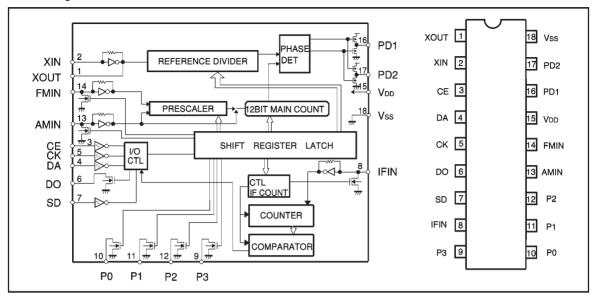

### Block diagram

# Pin descriptions

| Pin No. | Symbol          | Pin name             | Function                                                                                                                      | I/O            |  |

|---------|-----------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------|--|

| 1       | XOUT            | On satal annillation | For generation of standard frequency and internal clock.                                                                      | OUT            |  |

| 2       | XIN             | Crystal oscillation  | Connected to 7.2 MHz crystal resonator.                                                                                       | IN             |  |

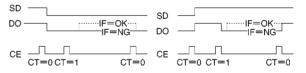

| 3       | CE              | Chip enable          | When CE is H, DA is synchronous with the rise of CK and                                                                       |                |  |

| 4       | DA              | Serial data          | read to the internal shift register. DA is then latched at the timing of the fall of CE. Also, output data is output from the | IN             |  |

| 5       | CK              | Clock signal         | CD terminal synchronous to the rise of CK.                                                                                    |                |  |

| 6       | DO              | Data out             | Comes ON during IF frequency detection or SD detection.                                                                       | Nch open drain |  |

| 7       | SD              | SD input             | SD signal is input. Observed by DO terminal.                                                                                  | IN             |  |

| 8       | IFIN            | IF input             | Input is for IF frequency.                                                                                                    | IIN            |  |

| 9       | P3              |                      |                                                                                                                               |                |  |

| 10      | P0              | Output nort          | Controlled on the basis of input date                                                                                         | Nob open ducin |  |

| 11      | P1              | Output port          | Controlled on the basis of input data.                                                                                        | Nch open drain |  |

| 12      | P2              |                      |                                                                                                                               |                |  |

| 13      | AMIN            | AM input             | Local input for AM                                                                                                            | IN             |  |

| 14      | FMIN            | FM input             | Local input for FM                                                                                                            | IN             |  |

| 15      | V <sub>DD</sub> | Power supply         | Power supply, with 4.0V to 6.0V applied voltage.                                                                              | _              |  |

| 16      | PD1             | Phase comparison     | High level when value obtained by dividing local output is                                                                    | 0              |  |

| 17      | PD2             | output               | higher than standard frequency. Low level when value is lower. High impedance when value is same.                             | 3-state        |  |

| 18      | Vss             | GROUND               | _                                                                                                                             | _              |  |

Audio ICs BU2616F

●Electrical characteristics (unless otherwise noted, Ta = 25°C, V<sub>DD</sub>1 = V<sub>DD</sub>2 = 5V)

| Parameter                    | Symbol           | Min.    | Тур.    | Max. | Unit | Condition                  | ns                               |

|------------------------------|------------------|---------|---------|------|------|----------------------------|----------------------------------|

| Power supply current         | IDD1             | _       | 6.0     | 10.0 | mA   | FMIN=130MHz, 100mVrms      |                                  |

| Quiescent current            | IDD2             | _       | 1.0     | 2.0  | mA   | No input,, PLL=OFF         |                                  |

| Input high level voltage     | VIH              | 4.0     | _       | _    | V    | CE, CK, DA terminals       |                                  |

| Input low level voltage      | VIL              | _       | _       | 1.0  | V    | CE, CK, DA terminals       |                                  |

| Input high level current 1   | IIH1             | _       | _       | 1.0  | μΑ   | CE, CK, DA terminals       | V <sub>IN</sub> =V <sub>DD</sub> |

| Input high level current 2   | IIH2             | _       | 0.3     | _    | μΑ   | XIN terminals              | VIN=VDD                          |

| Input high level current 3   | Іінз             |         | 6.0     | _    | μΑ   | FMIN, AMIN, IFIN termina   | als Vin=VDD                      |

| Input low level current 1    | IIL1             | -1.0    | _       | _    | μA   | CE, CK, DA terminals       | V <sub>IN</sub> =V <sub>SS</sub> |

| Input low level current 2    | lıL2             | _       | -0.3    | _    | μΑ   | XIN terminals              | V <sub>IN</sub> =V <sub>SS</sub> |

| Input low level current 3    | IILз             | _       | -6.0    | _    | μΑ   | FMIN, AMIN, IFIN termina   | als Vin=Vss                      |

| Output low level voltage 1   | V <sub>OL1</sub> | _       | 0.2     | 0.5  | V    | P0, P1, P2, P3, DO         | Io=1.0mA                         |

| Off level leakage current 1  | OFF1             | _       | _       | 1.0  | μA   | P0, P1, P2, P3, DO         | Vo=10V                           |

| Output low level voltage 2   | Vol2             | _       | 0.1     | 0.5  | V    | FMIN, AMIN, IFIN           | Ιουτ=0.1mA                       |

| Output high level voltage    | Vон              | VDD-1.0 | VDD-0.3 | _    | V    | PD1, PD2                   | Iουτ=-1.0mA                      |

| Output low level voltage     | Vol              | _       | 0.2     | 1.0  | V    | PD1, PD2                   | Ιουτ=1.0mA                       |

| Off level leakage current 2  | OFF2             | _       | _       | 100  | nA   | PD1, PD2                   | Vout=V <sub>DD</sub>             |

| Off level leakage current 3  | loff3            | -100    | _       | _    | nA   | PD1, PD2                   | Vout=Vss                         |

| Internal feedback resistor 1 | R <sub>F1</sub>  | _       | 10      | _    | МΩ   | XIN                        |                                  |

| Internal feedback resistor 2 | RF2              | _       | 500     | _    | kΩ   | FMIN, ANIN, IFIN           |                                  |

| Input frequency 1            | FIN1             | _       | 7.2     | _    | MHz  | XIN, sine wave, C coupling | 9                                |

| Input frequency 2            | FIN2             | 20      | _       | 130  | MHz  | FMIN, sine wave, C coupli  | ng VIN=50mVrms                   |

| Input frequency 3            | FIN3             | 0.4     | _       | 30   | MHz  | AMIN 1, sine wave, C cou   | pling VIN=70mVrms                |

| Input frequency 4            | FIN4             | 0.4     | _       | 16   | MHz  | IFIN, sine wave,C coupling | g VIN=70mVrms                    |

| Maximum input amplitude      | FINMAX           | _       | _       | 1.5  | Vrms | XIN,FMIN,AMIN,IFIN,sine    | wave,C coupling                  |

| Minimum pulse width          | TW               | _       | 1.0     | _    | μs   | CK, DA                     |                                  |

| Input rise time              | TR               | _       | _       | 500  | ns   | CE, CK, DA                 |                                  |

| Input fall time              | TF               | -       | _       | 500  | ns   | CE, CK, DA                 |                                  |

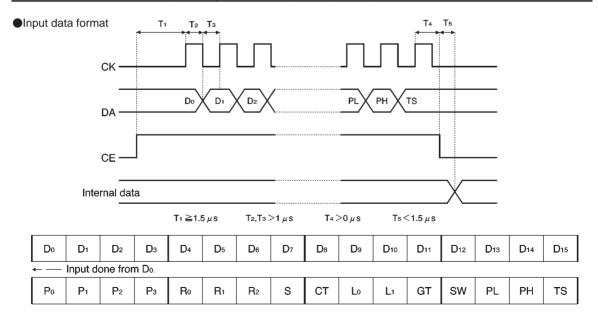

#### Input data format

Explanation of the data

(1) Division data: For  $D_0$  through  $D_{15}$  (When S=0, use  $D_4$  through  $D_{15}$ .)

Example: S = 0, SW = 0

When divide ratio = 1000, the actual set value is 500 since it passes through 1/2 the circuit. This translates to 1F4 (H) in HEX notation, and to (MSB) 0000 0001 1111 0100 (LSB) in binary notation. This data is used from LSB to D0 through D15.

| Do | D <sub>1</sub> | D <sub>2</sub> | Дз | D4 | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> | D8 | D <sub>9</sub> | D10 | D <sub>11</sub> | D <sub>12</sub> | D13 | D14 | D15 |

|----|----------------|----------------|----|----|----------------|----------------|----------------|----|----------------|-----|-----------------|-----------------|-----|-----|-----|

| 0  | 0              | 1              | 0  | 1  | 1              | 1              | 1              | 1  | 0              | 0   | 0               | 0               | 0   | 0   | 0   |

LSB

Example: S = 1, SW = 1

When divide ratio = 1000, the actual set value is 1000 since it does not pass through 1/2 the circuit. This translates to 3E8 (H) in HEX notation, and to (MSB) 0000 0011 1110 1000 (LSB) in binary notation. This data is used from LSB to D0 through D15.

| Do | D <sub>1</sub> | D2 | Дз | D4 | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> | D8 | D <sub>9</sub> | D10 | D <sub>11</sub> | D12 | D13 | D14 | D <sub>15</sub> |

|----|----------------|----|----|----|----------------|----------------|----------------|----|----------------|-----|-----------------|-----|-----|-----|-----------------|

| 0  | 0              | 0  | 1  | 0  | 1              | 1              | 1              | 1  | 1              | 0   | 0               | 0   | 0   | 0   | 0               |

Example: S = 1, SW = 0

When divide ratio = 1000, D0 through D3 can be anything since it does not pass through the prescalar. This translates to 3E8 (H) in HEX notation, and to (MSB) 0001 1111 0100 (LSB) in binary notation. This data is used from LSB to D0 through D15.

| Do | D <sub>1</sub> | D <sub>2</sub> | Dз | D4 | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> | D8 | D <sub>9</sub> | D10 | D <sub>11</sub> | D12 | D13 | D14 | D15 |

|----|----------------|----------------|----|----|----------------|----------------|----------------|----|----------------|-----|-----------------|-----|-----|-----|-----|

| Х  | Х              | Х              | Х  | 0  | 0              | 0              | 1              | 0  | 1              | 1   | 1               | 1   | 1   | 0   | 0   |

- (2) Output port control data: Po, P1, P2, P3

- 1: Nch open drain output ON

- 0: Nch open drain output OFF

- (3) R<sub>0</sub>, R<sub>1</sub>, R<sub>2</sub>, standard frequency data

|    | Data           |                |                    |

|----|----------------|----------------|--------------------|

| R∘ | R <sub>1</sub> | R <sub>2</sub> | Standard frequency |

| 0  | 0              | 0              | 25kHz              |

| 0  | 0              | 1              | 12.5kHz            |

| 0  | 1              | 0              | 6.25kHz            |

| 0  | 1              | 1              | 10kHz              |

| 1  | 0              | 0              | 5kHz               |

| 1  | 0              | 1              | 9kHz               |

| 1  | 1              | 0              | 1kHz               |

| 1  | 1              | 1              | * PLL OFF          |

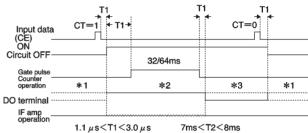

- (5) CT: Intermediate frequency measurement operation

- 1: Begins measurement.

- 0: Resets internal counter, IFIN goes to pulldown.

- (6) L0, L1: Setting of IF frequency detection amplitude

| S | LO | L1 | Frequency detection amplitude |

|---|----|----|-------------------------------|

| 0 | 0  | 0  | 10.70MHz±20kHz                |

| 0 | 0  | 1  | 10.65MHz±20kHz                |

| 0 | 1  | 0  | 10.75MHz±20kHz                |

| 0 | 1  | 1  | *                             |

| 1 | 0  | 0  | 450kHz±2.0kHz                 |

| 1 | 0  | 1  | 459kHz±2.0kHz                 |

| 1 | 1  | 0  | 450kHz±0.5kHz                 |

| 1 | 1  | 1  | 459kHz±0.5kHz                 |

- \*: Not used.

- \* FMIN = pulldown, AMIN = pulldown, PD = high impedance

- (4) S: switch between FMIN and AMIN

- 0: FMIN

- 1: AMIN

- (7) GT: Control of frequency measurement time0: 32ms

- 1: 64ms

- (8) SW: If this bit is set to ON while AMIN is selected, swallow counter division is possible.

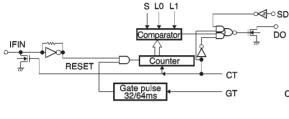

- •Intermediate frequency detection circuit and the DO output.

- (1) Structure

(9) PL PH: Control of charge pump output

PL = 0, PH = 0 PD1, PD2 go to PLL operation.

PL = 1, PH = 0 PD1, PD2 go to LO level.

PL = 0, PH = 1 PD1, PD2 go to HI level.

PL = 1. PH = 1 PD1. PD2 ao to LO level.

- (10) TS: Test data (0) is input

- (2) How the IF frequency detection circuit operates When control data CT is set to ON, the counter and the amp go into operation. When CT equals 0, the amp input pulldown counter is reset.

- (3) Explanation of the DO

- \*1 When the IF counter is OFF (CT = 0), SD input appears at the DO.

- \*2 When the IF counter is set to ON (CT = 1), the control system keeps it at LO level until the measurement is finished.

- \*3 After the measurement is finished, it goes to HI level if it is within the range of input frequency settings, and is kept at LO level if it is beyond the range of input frequency settings. When CT = 0, it returns to the conditions described under paragraph \*1.

# This datasheet has been downloaded from:

www. Data sheet Catalog.com

Datasheets for electronic components.