Motorola Preferred Device

TMOS POWER FET LOGIC LEVEL

> 50 AMPERES 60 VOLTS

RDS(on) = 0.028 OHM

## Advance Information **TMOS E-FET** ™ **Power Field Effect Transistors D2PAK for Surface Mount Logic Level TMOS (L2TMOS**™) N-Channel Enhancement-Mode Silicon Gate

These TMOS Power FETs are designed for high speed, low loss power switching applications such as switching regulators, converters, solenoid and relay drivers. This Logic Level Series part is specified to operate with level logic gate-to-source voltage of 5 volt and 4 volt.

- Silicon Gate for Fast Switching Speeds

- Low R<sub>DS</sub>(on) 0.028 Ω max

- Replace External Zener Transient Suppressor Absorbs High Energy in the Avalanche Mode

- Specially Designed Leadframe for Maximum Power Dissipation

- Available in 24 mm 13–inch/800 Unit Tape & Reel, Add T4 Suffix to Part Number

#

#### MAXIMUM RATINGS (T<sub>C</sub> = 25°C unless otherwise noted)

| Rating                                                                                                                                                                                                    | Symbol                                                   | Value             | Unit                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------|------------------------|

| Drain-Source Voltage                                                                                                                                                                                      | V <sub>DSS</sub>                                         | 60                | Vdc                    |

| Drain–Gate Voltage (R <sub>GS</sub> = 1.0 M $\Omega$ )                                                                                                                                                    | VDGR                                                     | 60                | Vdc                    |

| Gate-Source Voltage — Continuous                                                                                                                                                                          | V <sub>GS</sub>                                          | ±15               | Vdc                    |

| Drain Current — Continuous<br>— Continuous @ 100°C<br>— Single Pulse ( $t_p \le 10 \ \mu$ s)                                                                                                              | I <sub>D</sub><br>I <sub>D</sub><br>I <sub>DM</sub>      | 50<br>28<br>142   | Adc<br>Apk             |

| Total Power Dissipation<br>Derate above 25°C<br>Total Power Dissipation @ T <sub>A</sub> = 25°C, when mounted with the minimum recommended pad size                                                       | PD                                                       | 125<br>1.0<br>2.5 | Watts<br>W/°C<br>Watts |

| Operating and Storage Temperature Range                                                                                                                                                                   | TJ, Tstg                                                 | -55 to 150        | °C                     |

| Single Pulse Drain–to–Source Avalanche Energy — Starting T <sub>J</sub> = 25°C (V <sub>DD</sub> = 25 Vdc, V <sub>GS</sub> = 5.0 Vpk, I <sub>L</sub> = 50 Apk, L = 0.32 mH, R <sub>G</sub> = 25 $\Omega$ ) | E <sub>AS</sub>                                          | 400               | mJ                     |

| Thermal Resistance — Junction to Case<br>— Junction to Ambient<br>— Junction to Ambient, when mounted with the minimum recommended pad size                                                               | R <sub>θJC</sub><br>R <sub>θJA</sub><br>R <sub>θJA</sub> | 1.0<br>62.5<br>50 | °C/W                   |

| Maximum Lead Temperature for Soldering Purposes, 1/8" from case for 10 seconds                                                                                                                            | тլ                                                       | 260               | °C                     |

This document contains information on a new product. Specifications and information herein are subject to change without notice.

E–FET, Designer's and L<sup>2</sup>TMOS are trademarks of Motorola, Inc. TMOS is a registered trademark of Motorola, Inc. Thermal Clad is a trademark of the Bergquist Company

Preferred devices are Motorola recommended choices for future use and best overall value.

**REV 1**

**ELECTRICAL CHARACTERISTICS** (T<sub>1</sub> = 25°C unless otherwise noted)

| Cha                                                                                                                                              | racteristic                                                                                                           | Symbol              | Min     | Тур         | Max            | Unit         |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------|---------|-------------|----------------|--------------|

| OFF CHARACTERISTICS                                                                                                                              |                                                                                                                       |                     | -       | -           | -              |              |

| Drain–Source Breakdown Voltage<br>$(V_{GS} = 0 V, I_D = 250 \mu Adc)$<br>Temperature Coefficient (Positive)                                      |                                                                                                                       | V(BR)DSS            | 60<br>— |             | _              | Vdc<br>mV/°C |

| Zero Gate Voltage Drain Current<br>$(V_{DS} = 60 \text{ Vdc}, V_{GS} = 0)$<br>$(V_{DS} = 60 \text{ Vdc}, V_{GS} = 0, T_J = 125^{\circ}\text{C})$ |                                                                                                                       | IDSS                |         |             | 10<br>100      | μAdc         |

| Gate–Body Leakage Current (V <sub>GS</sub> = $\pm$ 15 Vdc, V <sub>DS</sub> = 0)                                                                  |                                                                                                                       | IGSS                | —       | —           | 100            | nAdc         |

| ON CHARACTERISTICS (1)                                                                                                                           |                                                                                                                       | •                   |         |             |                |              |

| Gate Threshold Voltage<br>(V <sub>DS</sub> = V <sub>GS</sub> , I <sub>D</sub> = 250 μAdc)<br>Temperature Coefficient (Negative)                  |                                                                                                                       | VGS(th)             | 1.0     | <br>4.78    | 2.0<br>—       | Vdc<br>mV/°C |

| Static Drain–Source On–Resistance<br>$(V_{GS} = 5.0 \text{ Vdc}, I_D = 25 \text{ Adc})$<br>$(V_{GS} = 4.0 \text{ Vdc}, I_D = 25 \text{ Adc})$    |                                                                                                                       | R <sub>DS(on)</sub> | _       | _           | 0.028<br>0.039 | Ohm          |

|                                                                                                                                                  | 5.0 Vdc)                                                                                                              | V <sub>DS(on)</sub> |         | _           | 1.68<br>1.40   | Vdc          |

| Forward Transconductance (V <sub>DS</sub> =                                                                                                      | = 15 Vdc, I <sub>D</sub> = 25 Adc)                                                                                    | 9FS                 | 17      | -           | _              | mhos         |

| DYNAMIC CHARACTERISTICS                                                                                                                          |                                                                                                                       |                     |         |             |                |              |

| Input Capacitance                                                                                                                                |                                                                                                                       | C <sub>iss</sub>    | _       | 3100        | 4340           | pF           |

| Output Capacitance                                                                                                                               | $(V_{DS} = 25 \text{ Vdc}, V_{GS} = 0, $<br>f = 1.0 MHz)                                                              | C <sub>oss</sub>    | _       | 1065        | 1491           |              |

| Reverse Transfer Capacitance                                                                                                                     |                                                                                                                       | C <sub>rss</sub>    | —       | 260         | 520            |              |

| SWITCHING CHARACTERISTICS (                                                                                                                      | 2)                                                                                                                    | •                   |         |             |                |              |

| Turn-On Delay Time                                                                                                                               |                                                                                                                       | <sup>t</sup> d(on)  | —       | 21          | 42             | ns           |

| Rise Time                                                                                                                                        | $(V_{DD} = 25 \text{ Vdc}, I_D = 50 \text{ Adc}, V_{GS} = 5.0 \text{ Vdc}, R_G = 9.1 \Omega)$                         | t <sub>r</sub>      | —       | 365         | 730            | 1            |

| Turn-Off Delay Time                                                                                                                              |                                                                                                                       | <sup>t</sup> d(off) | —       | 55          | 110            |              |

| Fall Time                                                                                                                                        |                                                                                                                       | tf                  | —       | 150         | 300            |              |

| Gate Charge                                                                                                                                      | (V <sub>DS</sub> = 48 Vdc, I <sub>D</sub> = 50 Adc,<br>V <sub>GS</sub> = 5.0 Vdc)                                     | QT                  | —       | 52          | 73             | nC           |

|                                                                                                                                                  |                                                                                                                       | Q <sub>1</sub>      | —       | 13          | —              |              |

|                                                                                                                                                  |                                                                                                                       | Q2                  | —       | 34          | —              |              |

|                                                                                                                                                  |                                                                                                                       | Q <sub>3</sub>      | —       | 27          | —              |              |

| SOURCE-DRAIN DIODE CHARACT                                                                                                                       | TERISTICS                                                                                                             |                     |         |             |                |              |

| Forward On–Voltage                                                                                                                               | (I <sub>S</sub> = 50 Adc, V <sub>GS</sub> = 0)<br>(I <sub>S</sub> = 50 Adc, V <sub>GS</sub> = 0, T <sub>J</sub> = °C) | V <sub>SD</sub>     |         | 1.52<br>1.1 | 2.5<br>—       | Vdc          |

| Reverse Recovery Time                                                                                                                            | (I <sub>S</sub> = 50 Adc, V <sub>GS</sub> = 0 ,<br>dI <sub>S</sub> /dt = 100 A/µs)                                    | t <sub>rr</sub>     | _       | 200         | _              | ns           |

| NTERNAL PACKAGE INDUCTANC                                                                                                                        | E                                                                                                                     |                     |         |             |                |              |

| Internal Drain Inductance<br>(Measured from the tab to center of die)                                                                            |                                                                                                                       | Ld                  | —       | 3.5         | —              | nH           |

| Internal Source Inductance<br>(Measured from the source lead 0.1" from package to source bond pad)                                               |                                                                                                                       | L <sub>S</sub>      | _       | 7.5         | _              | nH           |

Pulse Test: Pulse Width ≤ 300 μs, Duty Cycle ≤ 2%.

Switching characteristics are independent of operating junction temperature.

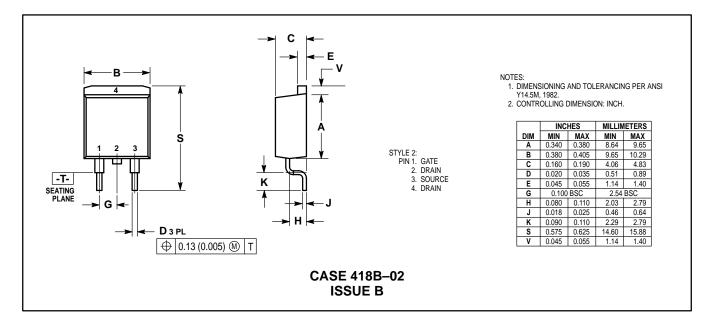

#### PACKAGE DIMENSIONS

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and **Motorola**, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### Literature Distribution Centers:

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. EUROPE: Motorola Ltd.; European Literature Centre; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England. JAPAN: Nippon Motorola Ltd.; 4–32–1, Nishi–Gotanda, Shinagawa–ku, Tokyo 141, Japan. ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.

$\Diamond$

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.